LLVM Mca : huawei HiSilicon's TSV110 work

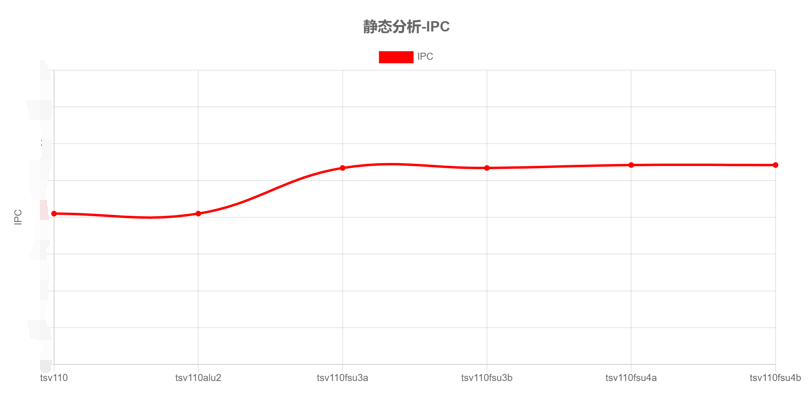

几个对比图¶

x轴的含义是改变port值的意思,比如tsv110alu2是在tsv110的基础上将alu的值改成2

相关的 git commit¶

commit c9ca3a3c66a493d72cf7afc7ee975e2de399f2e5

Author: Elvina Yakubova <[email protected]>

Date: Sat Nov 7 01:50:43 2020 +0300

[AArch64] Add driver tests for HiSilicon's TSV110

commit 93b99728b1676d23ab5dabc606344230d25e7f4b

Author: Elvina Yakubova <[email protected]>

Date: Sat Nov 7 01:22:35 2020 +0300

[AArch64] Add pipeline model for HiSilicon's TSV110

This patch adds the scheduling and cost model for TSV110.

Reviewed by: SjoerdMeijer, bryanpkc

Differential Revision: https://reviews.llvm.org/D89972

commit 123553921f86ac0fad7b742740aa45e8d380be02

Author: Bryan Chan <[email protected]>

Date: Fri Nov 9 19:32:08 2018 +0000

[AArch64] Support HiSilicon's TSV110 processor

Reviewers: t.p.northover, SjoerdMeijer, kristof.beyls

Reviewed By: kristof.beyls

Subscribers: olista01, javed.absar, kristof.beyls, kristina, llvm-commits

Differential Revision: https://reviews.llvm.org/D53908

llvm-svn: 346546

最近 Driver commit¶

复现上面的图¶

要改的地方¶

测试的汇编代码¶

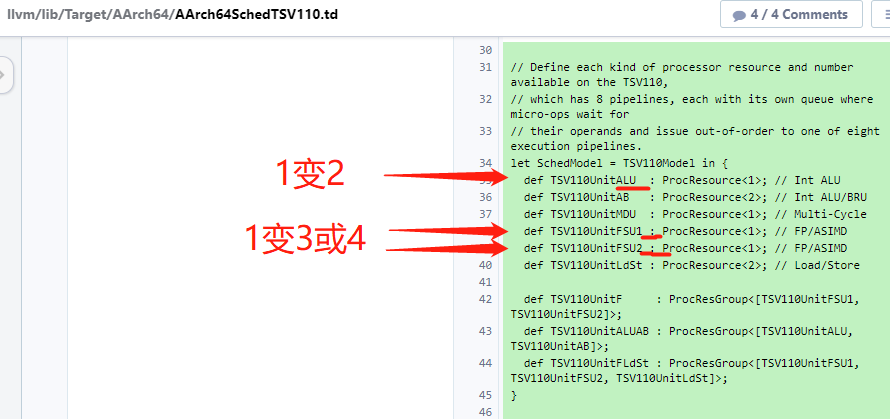

AArch64SchedTSV110.td¶

locate at llvm/lib/Target/AArch64/AArch64SchedTSV110.td

td file¶

tablegen(LLVM class) definitions

部分指令解释¶

BIC (bit clear) EON (Exclusive OR) ORR (OR operations on the values in Rn and Operand2)InstRW的定义

// Map a set of opcodes to a list of SchedReadWrite types. This allows

// the subtarget to easily override specific operations.

//

// SchedModel ties this opcode mapping to a processor.

class InstRW<list<SchedReadWrite> rw, dag instrlist> {

list<SchedReadWrite> OperandReadWrites = rw;

dag Instrs = instrlist;

SchedMachineModel SchedModel = ?;

// Allow a subtarget to mark some instructions as unsupported.

bit Unsupported = false;

}

def TSV110Wr_2cyc_1MDU : SchedWriteRes<[TSV110UnitMDU]> { let Latency = 2; }

class SchedWriteRes<list<ProcResourceKind> resources> : SchedWrite,

ProcWriteResources<resources>;

//定义TSV110上可用的每种处理器资源和数量,

//它有8条pipeline管道,每个管道都有自己的队列,微操作在那里等待

//它们的operands和issue将无序地发送到八个执行管道之一。

def TSV110UnitMDU : ProcResource<1>; // Multi-Cycle

需要进一步的研究学习¶

暂无

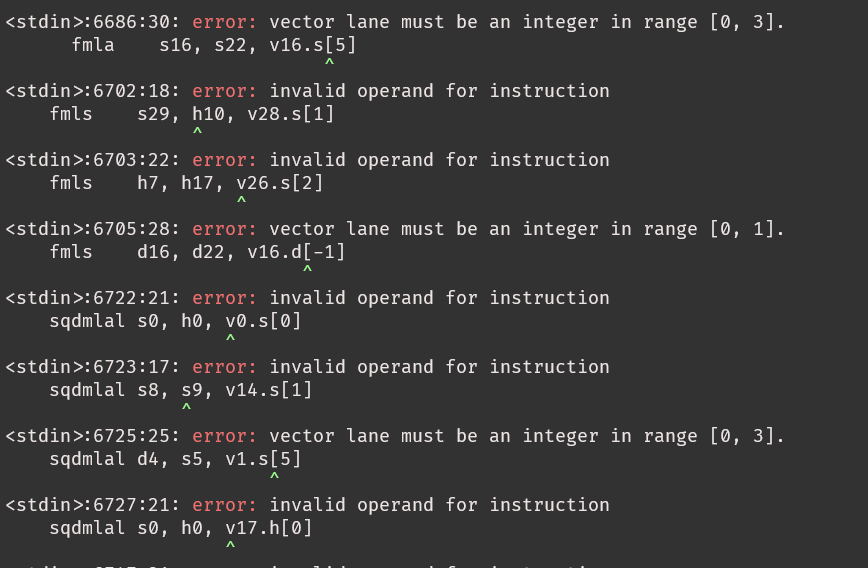

遇到的问题¶

暂无

开题缘由、总结、反思、吐槽~~¶

参考文献¶

无