Predictor

导言

What is address-based way predictor1

??? failure/success "Excellent Video Resource"

We're still on the lookout for an exceptional blog or overview paper to complement our understanding of this topic. Stay tuned for updates!

??? failure/success "Outstanding Blog or Overview Paper"

The key words are "rethink", "perspective"

cache way predictor¶

Motivation: energy and latency reduction

Set-associativecaches offer lower miss rates than direct-mapped caches, but usually have a longer access time(tag comparator).(1)

The energy consumption of set-associative cache tends to be higher than that of direct-mapped cache, because all the ways in a set are accessed in parallel although at most only one way has the desired data.

way-predicting set-associative cache improves the ED (energy-delay) product by 60-70% compared to a conventional set-associative cache.5

- the access time for a two-way associative cache is 51%,46% and 40% times longer than the access time for a direct mapped cache for 8KB, 16KB and 32KB caches, respectively2

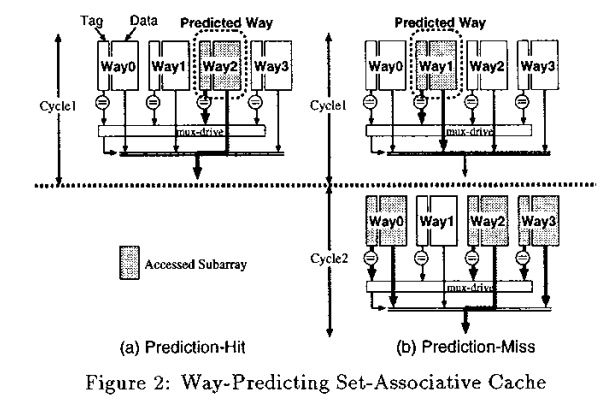

The way-predicting cache speculatively chooses one way before starting the normal cache-access process, and then accesses the predicted way as shown in Figure 2(a).

If the prediction is correct, the cache access has been completed successfully. Otherwise, the cache then searches the other remaining ways as shown in Figure 2(b).

algorithms¶

- MRU (Most Recently Used) algorithm for the way prediction5. Reading the MKU information before starting the cache access might make cache access time longer. However, it can be hidden by calculating the set-index address at an earlier pipe-line stage2

further explored¶

We design an address-based way predictor as they have been shown to achieve high accuracy for pages234

参考文献¶

-

PACT'17 Near-Memory Address Translation ↩

-

B. Calder, D. Grunwald, and J. S. Emer, “Predictive sequential associative cache,” in Proceedings of the 1996 International Symposium on High-Performance Computer Architecture, 1996 ↩↩↩

-

M. D. Powell, A. Agarwal, T. N. Vijaykumar, B. Falsafi, and K. Roy, “Reducing set-associative cache energy via way-prediction and selective direct-mapping,” in Proceedings of the 2001 International Symposium on Microarchitecture, 2001. ↩

-

D. Jevdjic, G. H. Loh, C. Kaynak, and B. Falsafi, “Unison cache: A scalable and effective die-stacked DRAM cache,” in Proceedings of the 2014 Annual International Symposium on Microarchitecture, 2014. ↩

-

Way-Predicting Set-Associative Cache for High Performance and Low Energy Consumption 1999 ↩↩