Gem5

简介¶

- GEM5是一款模块化的离散事件驱动全系统模拟器,由C++与python编写

- 它结合了M5(多处理器模拟器)和GEMS(存储层次模拟器)中最优秀的部分,是一款高度可配置、集成多种ISA和多种CPU模型的体系结构模拟器。

- M5是由Michigan大学开发的一款开源的多处理机模拟器,受到了业内的广泛关注,很多高水平论文都采用M5作为研究工具。

- 另一方面,Wisconsin推出的GEMS能够对储存层次进行详细而灵活的模拟,包括对多种不同的cache一致性协议和互联模型的支持。

- 目前的GEM5是M5和GEMS的一个紧耦合版本。

- GEM5已经能够支持多种商用ISA,包括X86、ARM、ALPHA、MIPS、Power、SPARC等,并且能够在X86、ARM、ALPHA上加载操作系统。

可选配置(灵活性)¶

- 灵活性是指gem5提供了多种CPU模型、系统模型以及存储器模型。

- CPU模型:Atomic、Timing、In-order、O3(Out of Order)。

AtomicSimple是最简单规模的模型,一个cycle完成一条指令的执行,memory 模型比较理想化,访存操作为原子性操作。适用于快速功能模拟。TimingSimple模拟器也是无流水线的模拟,但是使用了存储器访问时序模型,用以统计存储器访问延迟。In-Order模型是GEM5模拟的新特性,强调指令时序与仿真精度,流水级为默认五级流水:取值、译码、执行、访存、写回。并且模拟了cache部件、执行部件、分支预测部件等。O3模拟器是流水级模拟,O3模拟器模拟了乱序执行和超标量执行的指令间依赖,以及运行在多CPU上的并发执行的多线程。- 默认7级流水:取值、译码、重命名、发射、执行、写回、提交。

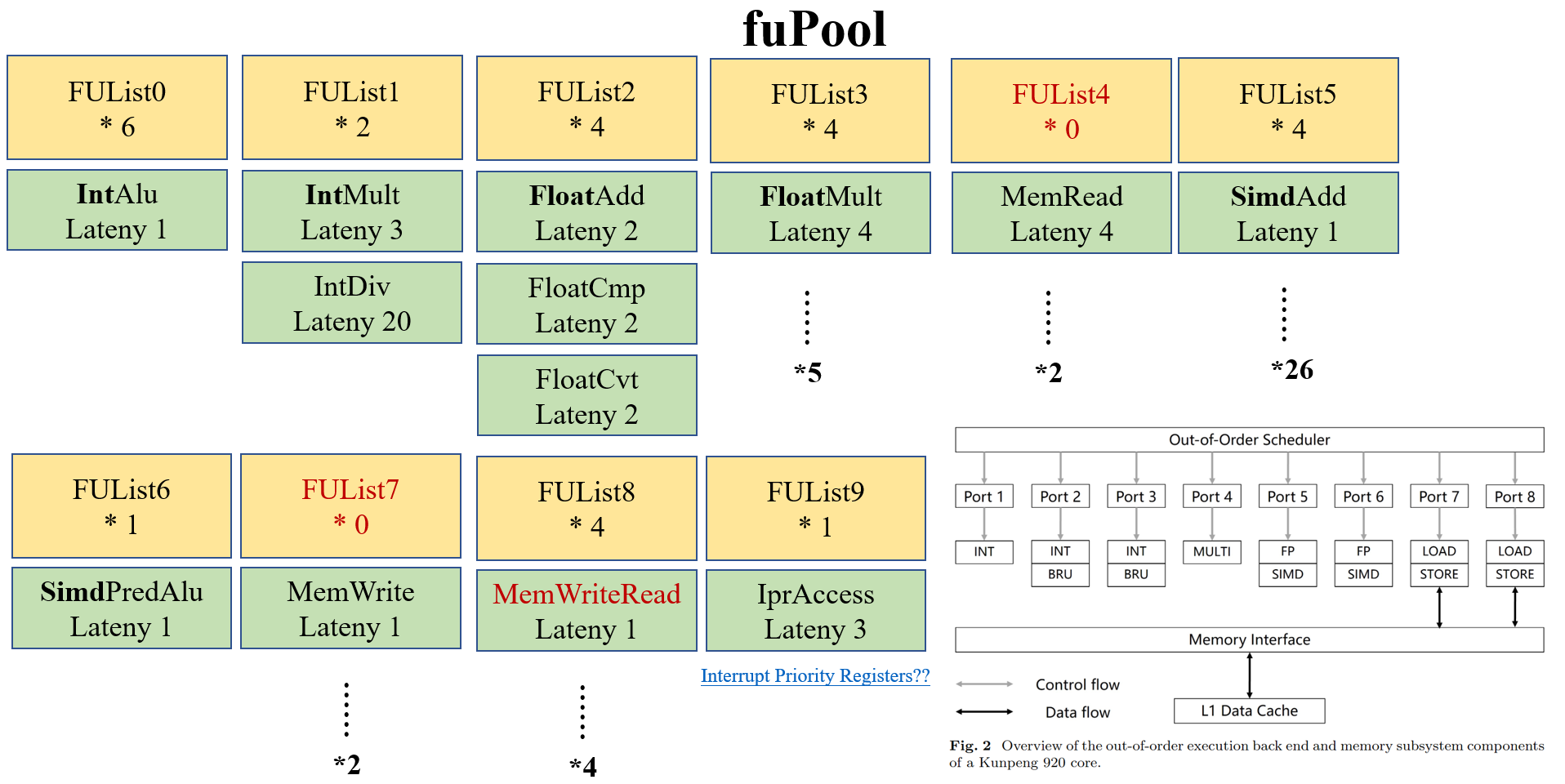

- 模拟了物理寄存器文件、IO、LSQ、ROB功能部件池等。

- 主要参数为流水管道间延迟、硬件线程数、IQ/LSQ/ROB项数、FU延迟、物理寄存器重命名、分支预测、访存依赖预测等。

- 系统模型:SE(System-call emulation)、FS(Full System)。

- 存储模型:Classic、Ruby。

- M5的Classic mode存储器是最简单的模型,它提供了简洁快速的可配置性。

- GEMS的Ruby模型注重于精确度并且支持不同的cache一致性协议。

- Ruby存储模型支持庞大阵列的互联拓扑,包括两个不同的网络模型:Simple网络与Garnet网络。

- Simple网络对链路、路由延迟与链路带宽进行建模,但并不建模路由资源竞争与流控。

- Garnet网络详细建模路由微架构,包括所有相关的资源竞争与流控时序。

基本模式¶

- System Call Emulation (SE) Mode

- In this mode, one only needs to specify the binary file to be simulated. This binary file can be statically/dynamically linked.

- full-system mode

- This mode simulates a complete system which provides an operating system based simulation environment.

- very slow, rendering it impractical for deployment in real-world applications.

time ./build/ARM/gem5.fast configs/example/se.py --cmd=/home/shaojiemike/test/llvmVSgem5/MV/MV_gem5 -n 32 --cpu-type=O3CPU --l1d_size=64kB --l1i_size=16kB --caches

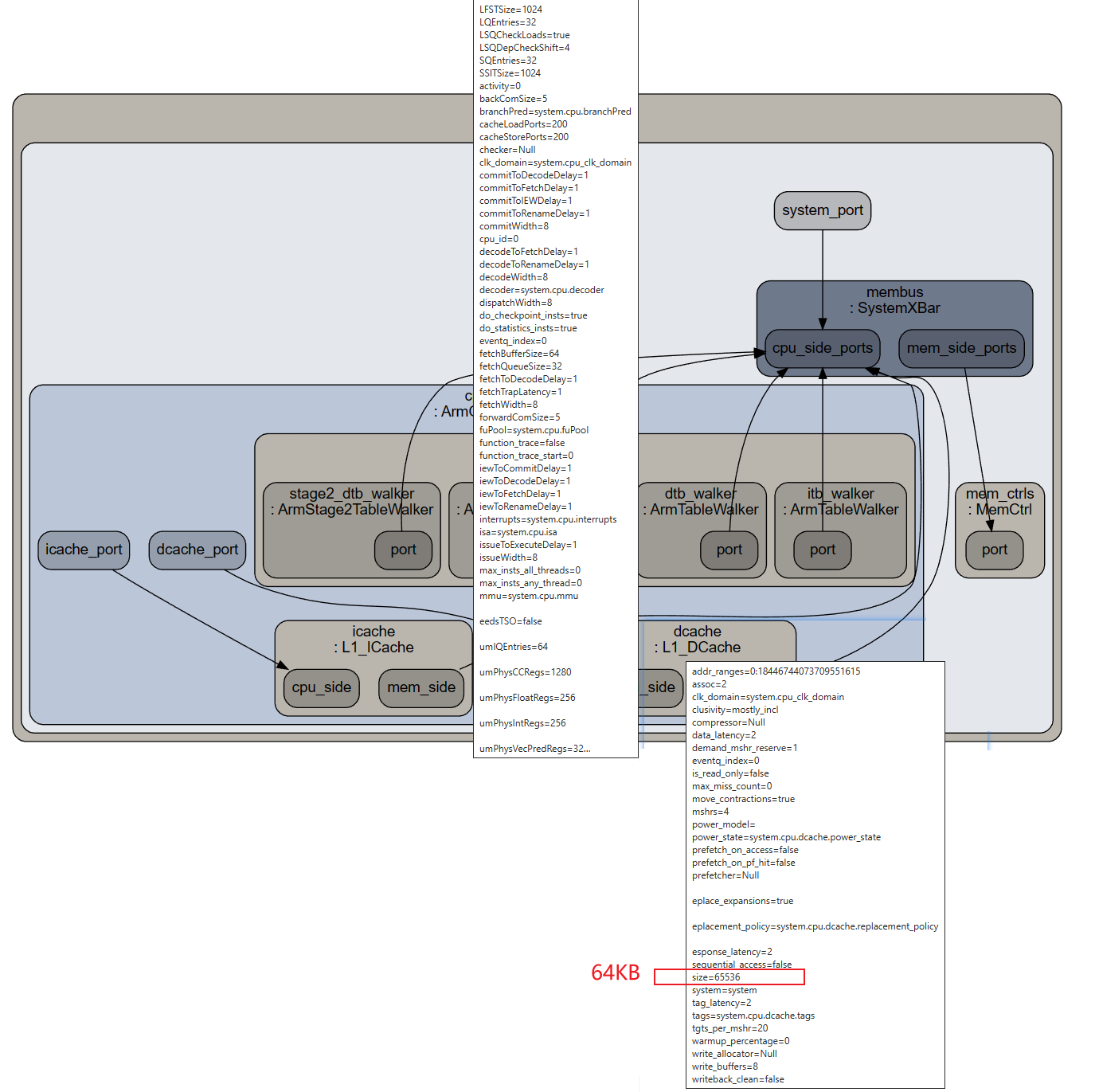

- L1d cache是每个核单独64KB(原因见后图)。但其实默认cache结构是L2共享的

安装¶

- 在源目录下运行

scons build/<config>/<binary>建立模拟器。 <config>gem5的配置文件,如ARM,X86等<binary>模拟器的类型,有如下gem5.debug有关闭了优化,使gdb一类的工具更易于调试;gem5.opt有打开优化,但保留了调试输出和断言;gem5.fast去除了调试工具;gem5.prof用于与gprof共同使用

输入参数¶

gem5 安装的默认配置¶

可选选项在./build/ARM/gem5.fast configs/example/se.py -h或者 configs/common/Options.py 中查看

常规的配置:

- 多级cache

- CPU

- 频率,核数

- 指令发射宽度

- commitWidth, decodeWidth, dispatchWidth, fetchWidth, issueWidth,

- renameWidth, squashWidth, wbWidth ,

- 端口模型的部件类型以及个数

- 内存

cache設置¶

- 只指定大小是沒用的,需要在L1cache 前加上 “--caches”,在l2cache前加上 “--l2cache“。命令結果類似

- 默认cache是没有开硬件预取HWP的,类型通过

--list-hwp-types查看。可以指定L1L2cache的HWP类型,如--l1d-hwp-type=TaggedPrefetcher。

build/X86/gem5.opt configs/example/se.py

--caches --l1d_size=32kB --l1i_size=32kB

--l2cache --l2_size=256kB

--l3_size=8192kB # l3 在 se里是不生效的

-c tests/test-progs/hello/bin/x86/linux/hello

# 建议将L3大小并入L2来模拟cycle的下限

build/X86/gem5.opt configs/example/se.py

--caches --l1d_size=32kB --l1i_size=32kB

--l2cache --l2_size=256kB+8192kB

-c tests/test-progs/hello/bin/x86/linux/hello

进阶配置:

输出文件¶

运行完SE模式,默认会在指令路径下生成m5out文件夹,其中各文件大致含义如下:

config.ini或者config.json运行指令的系统参数- Contains a list of every SimObject created for the simulation and the values for its parameters.

json格式的文件能比较好的理清config的重要设置[system.cpu]有CPU的具体设置[system.mem_ctrls.dram]有DRAM读取数据的具体设置[system.membus]BUS的相关设置stats.txt模拟结果数据(具体的周期数等)- A text representation of all of the gem5 statistics registered for the simulation.

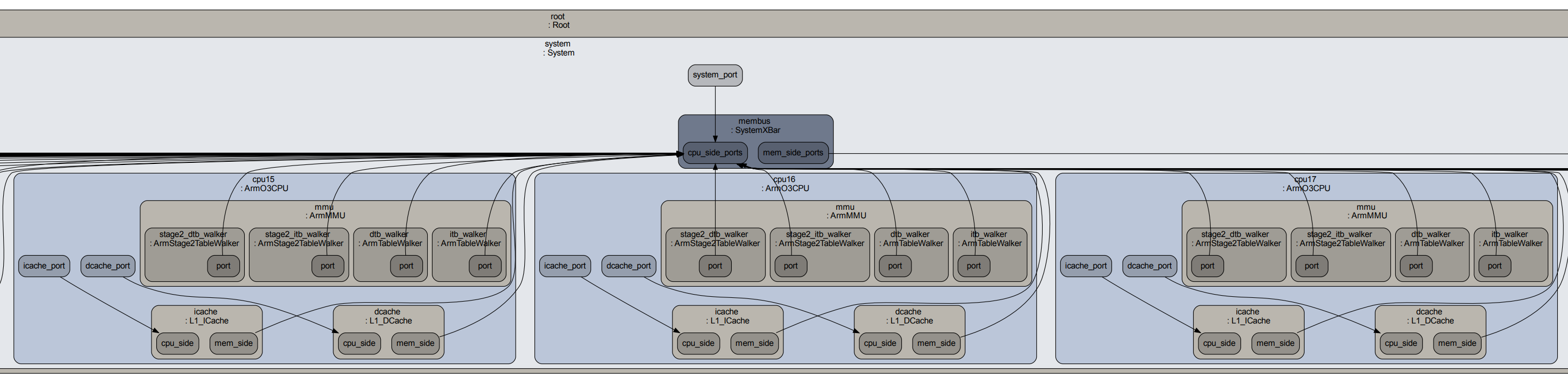

system.clk_domain.clock 1000 # Clock period in ticks (Tick)system.cpu_clk_domain.clock 500 # Clock period in ticks (Tick)fs/proc/lscpu模拟系统配置(类似lscpu)config.dot.*模拟的系统结构config.dot是以文字展示config.dot.pdf和config.dot.svg都是以图片表示

config.dot.svg能展示每个部件的细节参数

运行¶

CPU参数解释¶

各阶段发射宽度¶

commitWidth, decodeWidth, dispatchWidth, fetchWidth, issueWidth, renameWidth, squashWidth, wbWidth

下面是行数占比最大的几个部分

branchPred¶

- BTBEntries

decoder¶

fuPool¶

gem5 模拟器误差来源分析¶

运行真实周期数¶

- 使用

perf stat test.exe, 可参考本博客perf文章

需要进一步的研究学习¶

暂无

遇到的问题¶

暂无