Static Code Analysis

静态代码分析器的意义¶

在不运行程序的情况下,预测程序性能表现。得到估计时钟周期,资源占用情况,潜在的代码瓶颈等的分析。以便优化程序,或者为了更好的运行程序反过来对CPU的架构设计提出意见。

在预测的过程中,也会简单进行自动向量化,指令调度等工作。

比如你想看在arm架构下该程序下有什么瓶颈,但是你只有intel的机器,你就可以通过静态代码分析器来分析。但是当前的效果都不是太好。

已有的Static Code Analyzer¶

IACA¶

IACA (the Intel Architecture Code Analyzer) is a (2019: end-of-life) freeware, closed-source static analysis tool made by Intel

由于Intel对自己的处理器优化很了解,所有可以更好的预测。 比如 zero-idioms 和 micro-op fusions(聚合,将相邻指令变为一条指令)

zero-idioms —— The processor recognizes that certain instructions are independent of the prior value of the register if the two operand registers are the same. An instruction that subtracts a register from itself will always give zero, regardless of the previous value of the register.

Ithemal¶

Ithemal (Instruction THroughput Estimator using MAchine Learning) 基于hierarchical LSTM–based 方法。基本块预测器,但是是黑盒。

Long short-term memory (LSTM) is an artificial recurrent neural network (RNN) architecture used in the field of deep learning.

应该是准确度最高的

LLVM-mca¶

LLVM Machine Code Analyzer

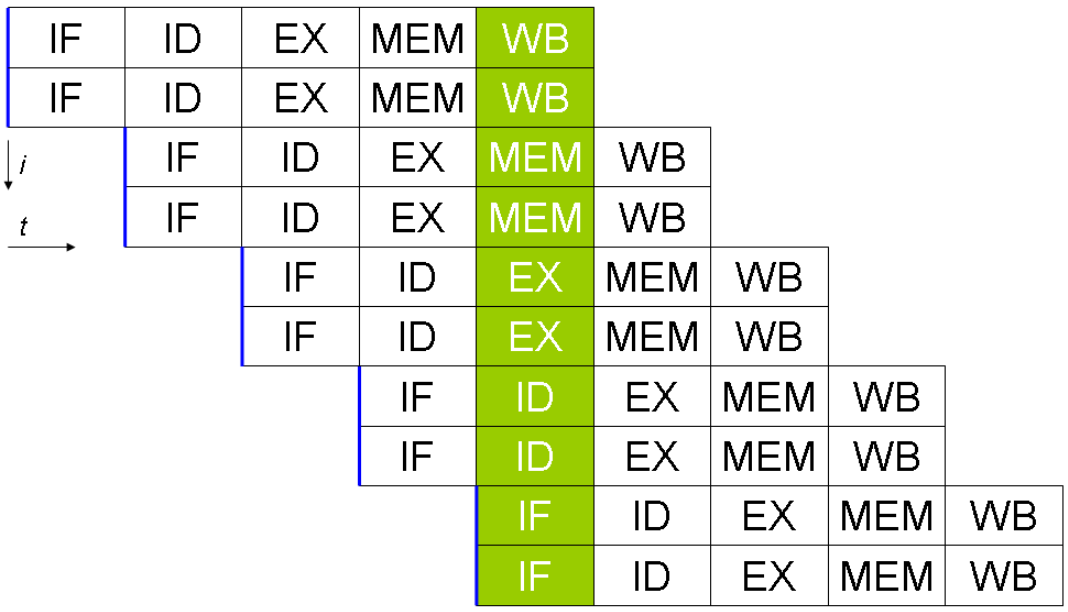

受到IACA启发的相似的工具,是乱序超标量(多条流水线,每周期可以完成2条以上指令,如下图)微架构模拟器。

使用了LLVM后端的调度模型参数。这种重用调度模型的选择对llvm cost 模型提供了经验。其准确性于调度模型有关。

使用了LLVM后端的调度模型参数。这种重用调度模型的选择对llvm cost 模型提供了经验。其准确性于调度模型有关。

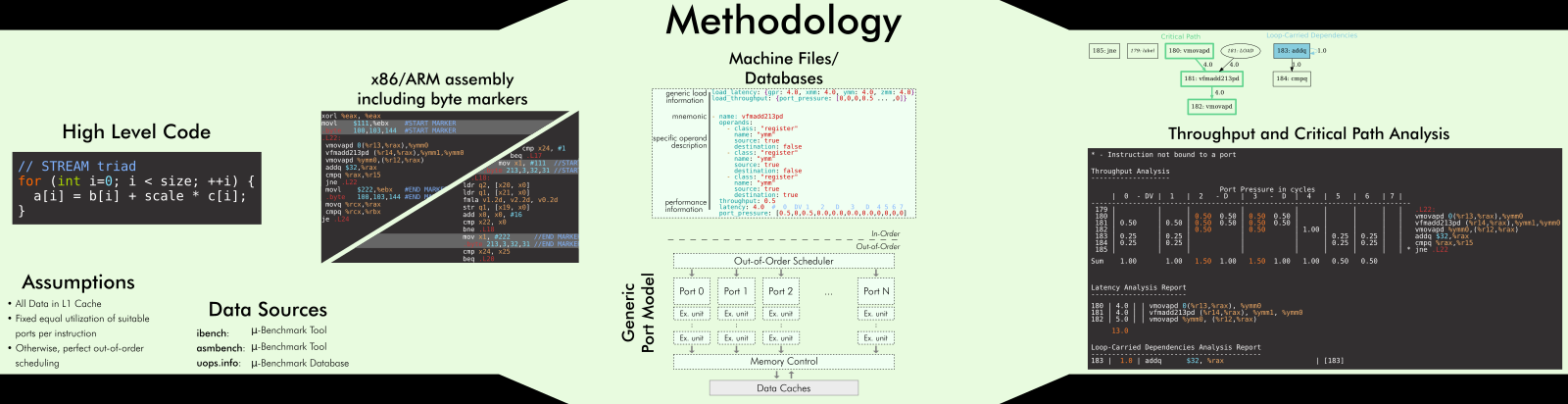

OSACA¶

Open Source Architecture Code Analyzer

是IACA的开源替代,也和llvm-mca很像。是参数化的乱序模拟器,但是参数来自测量的指令查找表

cost model¶

LLVM 和GCC 也有cost model,但是是指令层面的,不是基本块层面的。

比如LLVM 至少有3个: 1. a generic, per-instruction IR (Intermediate Representation) cost model for its target-independent optimizations 2. one for instruction scheduling (the scheduling model [14] is also used by llvm-mca); 3. another one for register allocation

基本概念¶

throughput¶

Predicting the (average) number of clock cycles a processor takes to execute a block of assembly instructions in steady state

performance models / Processor performance models¶

指代静态代码分析器,就是别名。

需要进一步的研究学习¶

暂无

遇到的问题¶

暂无

开题缘由、总结、反思、吐槽~~¶

参考文献¶

https://github.com/RRZE-HPC/OSACA