Wake Up Process

Linux 多进程的竞争休眠机制

基本是基于Linux的时间片轮转机制。A process/thread is woken up by inserting it in the queue of processes/threads to be scheduled.

内核调度算法

CFS(Completely Fair Scheduler)是一种用于 Linux 操作系统的调度算法,它旨在实现对 CPU 时间的公平分配。CFS 是 Linux 内核中默认的调度器,自 Linux 2.6.23 版本以来就成为了标准调度器。

CFS 调度算法的主要目标是确保各个任务在相同的时间片内能够获得公平的CPU时间,不会因为优先级等因素而造成资源争夺不均。以下是 CFS 调度算法的一些关键特点和原则:

-

虚拟化时钟: CFS 使用了一种称为虚拟化时钟(virtual runtime)的概念,而不是传统的时间片。每个任务都有一个虚拟运行时间,调度器根据虚拟运行时间来决定哪个任务应该被调度。

-

权重: CFS 引入了权重的概念,用于调整不同任务的相对优先级。较高权重的任务会在相同时间间隔内获得更多的虚拟运行时间,从而实现按比例分配CPU资源。

-

累积虚拟运行时间: 调度器会根据每个任务的权重和已累积的虚拟运行时间,计算出每个任务的应有的虚拟运行时间片。任务在使用完它的时间片后,会根据虚拟运行时间进行重新排队。

-

红黑树结构: CFS 使用红黑树来管理任务队列,这种数据结构使得在插入、删除和搜索任务时的时间复杂度保持在对数级别。

除了 CFS,Linux 内核还有其他调度算法,如:

-

实时调度器(Real-Time Scheduler): 用于实时任务,提供硬实时和软实时的调度策略,确保实时任务在指定的时间内执行完成。

-

O(1) 调度器(O(1) Scheduler): 是 Linux 2.4 内核中使用的调度器,它的时间复杂度为常数级别。然而,随着多核系统的出现,O(1) 调度器在多核环境下的性能表现受到限制,因此被 CFS 替代。

这些调度算法在不同的场景和需求下,对于多任务操作系统的调度提供了不同的方法和策略。选择适合的调度算法可以根据系统的应用和性能要求来进行。

问题

在高强度竞争之后,有些进程陷入长期sleep,并且在核空闲的时候,也不再重新运行?为什么?

原因可能是程序逻辑阻塞了,或者在等待IO

查看进程Sleep的原因

首先 计算机对一个进程是如何判断sleep的,是某时间内的计算占比低于某个阈值吗?

htop s 可以查看kernel 是不是阻塞, l 可以查看是不是读写同一个文件导致阻塞了。

Sleep的瓶颈在哪里

sleep for what, waiting for what?

实践1 strace

strace -p PID 可以显示一些信息

$ strace -p 4005042

wait4(-1, # 等待任意子进程结束

# check subprocess

$ pstree -p 4005042

pinbin(4005042)---BC_Compute(4005082)-+-{BC_Compute}(4005187)

|-{BC_Compute}(4005188)

|-{BC_Compute}(4005252)

|-{BC_Compute}(4005296)

|-{BC_Compute}(4005299)

`-{BC_Compute}(4005302)

$ strace -p 4005082

strace: Process 4005082 attached

futex(0x7fffe52de1b8, FUTEX_WAIT, 2, NULL

# futex - fast user-space locking(seems to be used in OpenMP)

# It is typically used as a blocking construct in the context of shared-memory synchronization.

$ strace -p 4005188

nanosleep({tv_sec=0, tv_nsec=2000000}, 0x7fffe5368bc0) = 0 # repeat

nanosleep({tv_sec=0, tv_nsec=2000000}, 0x7fffe536dbc0) = 0

It seems this is a subprocess repeating sleep leading to all other process to wait in the synchronization.

Use gdb -p PID to attach the process to locate the infinite loop (need Debug Symbols).

futex解释

futex 是 Linux 下的一个系统调用,用于实现用户空间线程间的同步和通信。让我们逐个解释这个系统调用中的每个参数的含义:

0x7fffe52de1b8: 这是一个指向内存地址的指针(或称为地址),通常是用于表示需要同步的资源或变量的地址。在这里,它表示需要等待的共享资源或变量的地址。FUTEX_WAIT: 这是一个指定 futex 要执行的操作的标志。FUTEX_WAIT表示线程正在等待 futex 的值发生变化,即等待条件满足。当某个线程执行FUTEX_WAIT操作时,如果 futex 的值与预期不符,则该线程将被置于休眠状态,直到 futex 的值发生变化或超时。2: 这是一个表示期望的 futex 值的参数。当调用FUTEX_WAIT时,线程将检查 futex 的当前值是否等于此参数指定的值。如果不等于,则线程将休眠等待。NULL: 这是一个指向 timespec 结构的指针,用于设置超时。这里为NULL表示调用没有设置超时,即线程将一直等待,直到 futex 的值发生变化。

总的来说,futex(0x7fffe52de1b8, FUTEX_WAIT, 2, NULL) 表示线程正在等待位于内存地址 0x7fffe52de1b8 的 futex 变量的值等于 2。如果 futex 的值不是 2,则线程将一直等待直到 futex 的值变为 2 或者超时。这样的同步机制在多线程编程中用于等待条件满足后再执行某些操作,从而避免资源竞争和提高程序的并发性能。

nanosleep解释

这是一个系统调用 nanosleep 的输出,通常用于让线程休眠一段时间。让我们逐个解释这个系统调用的含义:

-

nanosleep: 这是 Linux 下的一个系统调用,用于使线程休眠一段指定的时间。 -

{tv_sec=0, tv_nsec=2000000}: 这是传递给nanosleep的第一个参数,是一个指向timespec结构的指针。timespec结构用于表示时间间隔,包括秒(tv_sec)和纳秒(tv_nsec)。

在这里,tv_sec=0 表示秒数为 0,tv_nsec=2000000 表示纳秒数为 2000000。因此,这个 nanosleep 调用将会使线程休眠 2 毫秒(1 秒 = 1000000000 纳秒,所以 2000000 纳秒就是 2 毫秒)。

-

0x7fffe5368bc0: 这是传递给nanosleep的第二个参数,表示一个timespec结构的指针。这个参数用于存放未休眠完成的剩余时间,如果nanosleep被中断(例如收到信号),它将在这个指针中返回剩余的时间。在这个输出中,剩余时间被存储在内存地址0x7fffe5368bc0处。 -

= 0: 这是nanosleep的返回值,表示成功完成。返回值为 0 表示nanosleep成功休眠了指定的时间。

综上所述,这个输出表示线程成功休眠了 2 毫秒。

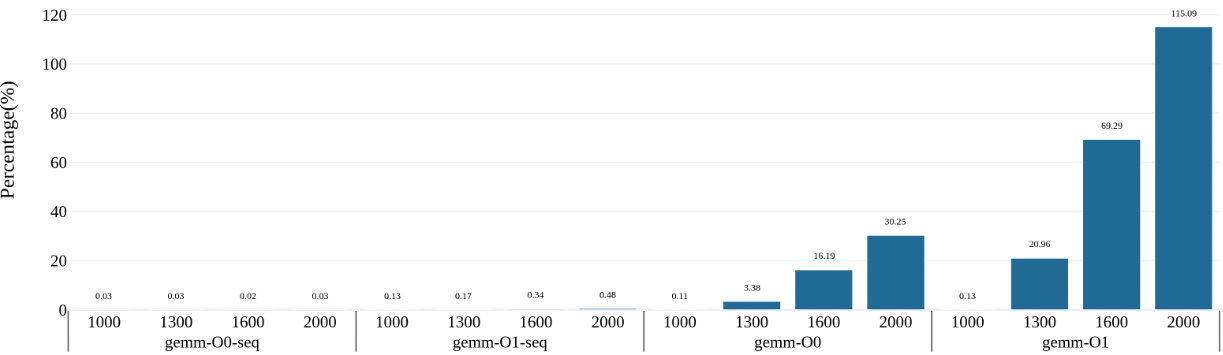

实践2: zsim模拟程序

程序直接执行正常,zsim模拟直接sleep?

$ strace -p 303359

read(10,

$ pstree -p 303359 │

gups_vanilla(303359)-+-gups_vanilla(303449)-+-orted+ │

| `-{gups+ │

|-{gups_vanilla}(303360) │

|-{gups_vanilla}(303361)

$ pstree -p 303449 │

gups_vanilla(303449)-+-orted(303451)-+-{orted}(303452) │

| |-{orted}(303642) │

| |-{orted}(303643) │

| `-{orted}(303644) │

`-{gups_vanilla}(303450)

这是一个 Open MPI(Message Passing Interface)的启动命令,用于启动一个 MPI 程序,并配置一些运行时参数。让我们逐个解释这个命令中的每个选项和参数的含义:

orted --hnp --set-sid --report-uri 11 --singleton-died-pipe 12 -mca state_novm_select 1 -mca ess hnp -mca pmix ^s1,s2,cray,isolated

部分参数含义如下:

orted: 这是 Open MPI 的一个工具,用于启动和管理 MPI 进程。-mca state_novm_select 1: 这是一个 MCA(Modular Component Architecture)选项,用于指定某个模块或组件的参数设置。在这里,state_novm_select设置为 1,可能是指定某个组件或模块在运行时的选项。-mca pmix ^s1,s2,cray,isolated: 这是另一个 MCA 选项,用于配置 PMIx(Process Management Interface for Exascale)的相关设置。^s1,s2,cray,isolated表示排除 s1、s2、cray 和 isolated 这些模块,可能是禁用某些特定的组件或功能。

| pid | strace output | explanation |

|---|---|---|

| 303451 | restart_syscall(<... resuming interrupted read ...> | |

| 303452 | futex(0xabba001ec8, FUTEX_WAIT, 2, NULL | |

| 303642 | epoll_wait(18, ... | epoll_wait 系统调用,用于等待文件描述符18上的事件 |

| 303643 | select(50, [48 49], NULL, NULL, | 如下 |

| 303644 | select(53, [51 52], NULL, NULL, |

restart_syscall表示系统调用被中断后重新启动的过程。它通常出现在系统调用的执行过程中,当某个信号(例如 SIGSTOP 或 SIGCONT)中断了系统调用的执行,然后系统调用在信号处理完成后被重新启动。- select 是一个用于在多个文件描述符上进行 I/O 多路复用(I/O multiplexing)的系统调用,它可以监视多个文件描述符,并在其中任何一个文件描述符准备好进行 I/O 操作时返回。

- select 调用的输出,它将监视文件描述符 48 和 49,并在其中任何一个文件描述符准备好读取数据或超时(2 秒后)时返回。

- 完全无法理解呢! 可能需要深入了解MPI的实现栈细节才能明白。

命令行唤醒Sleep进程

The only way to “wake it up” is to arrange for the condition to be met. 用户是无法更改的状态的。

传统kill进程

需要进一步的研究学习

暂无

遇到的问题

暂无

开题缘由、总结、反思、吐槽~~

参考文献

上面回答部分来自ChatGPT-3.5,没有进行正确性的交叉校验。

无