一种新的profiler,可以profile没有用户干预的内存访问的基本块。

基于这种profiler创建了BHive,来验证llvm-mca等模型。

BHive是用来评价llvm-mca这些模型的,实验基于各种收集来的一个基本块各种评价

困难在于现有的 没有考虑 memory crash ??? .默认命中L1 cache

A key technical challenge with collecting a large basic block dataset is that there is no existing approach to profile an arbitrary basic block that has been removed from its program

context.

(没懂?那为什么要removed from its program

context) 因为要把常用的应用拆成小例子来评判,这些模型的准确性。

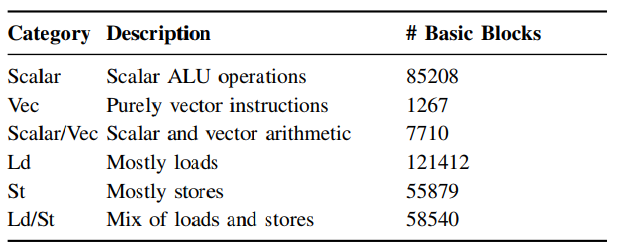

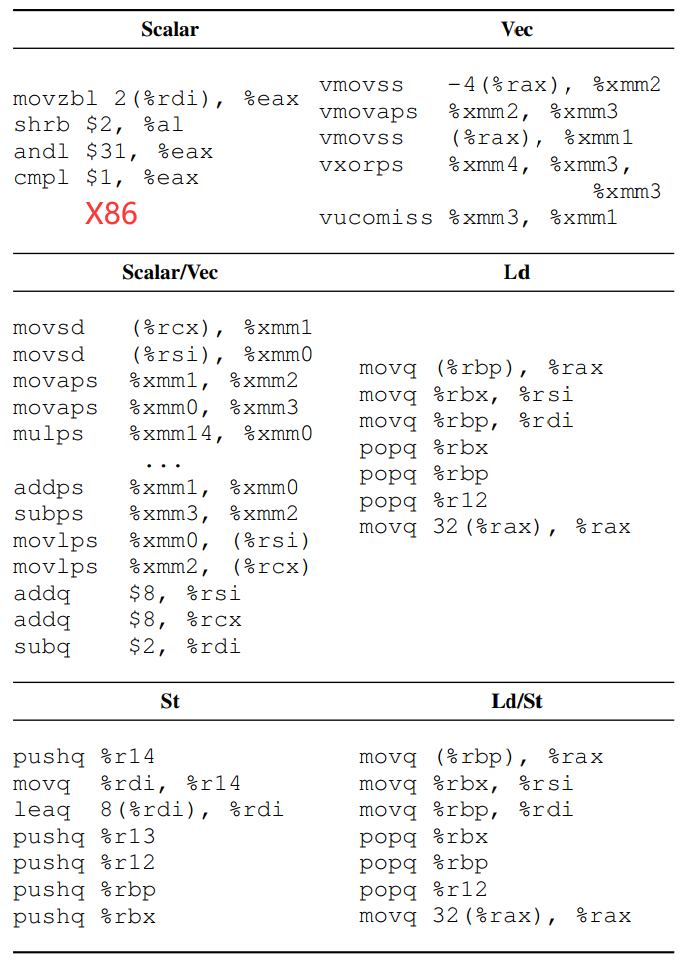

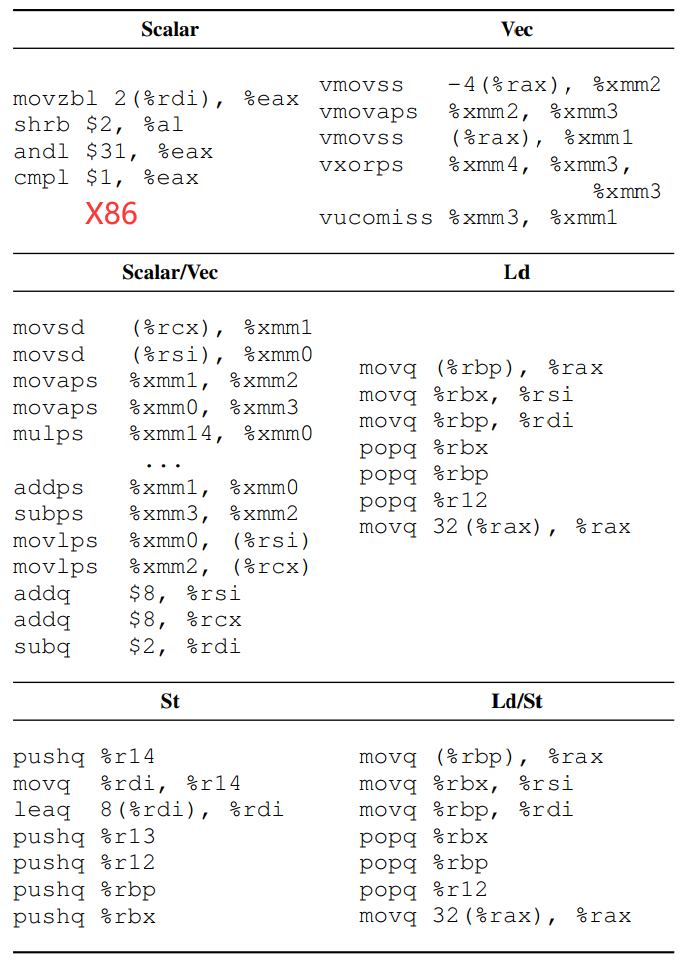

运用隐含狄利克雷分布LDA,基于cpu资源的利用率,来cluster benchmark suite里的基本块

通过对各种类型最基本的代码块来进行profile,从而形成针对各种performance model的数据库。

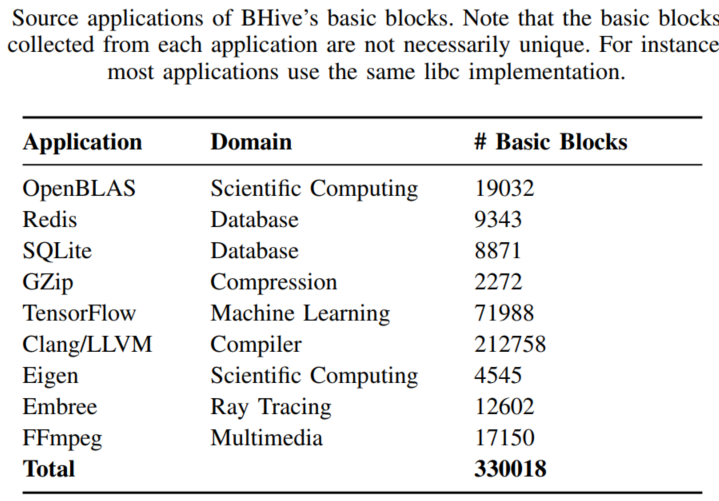

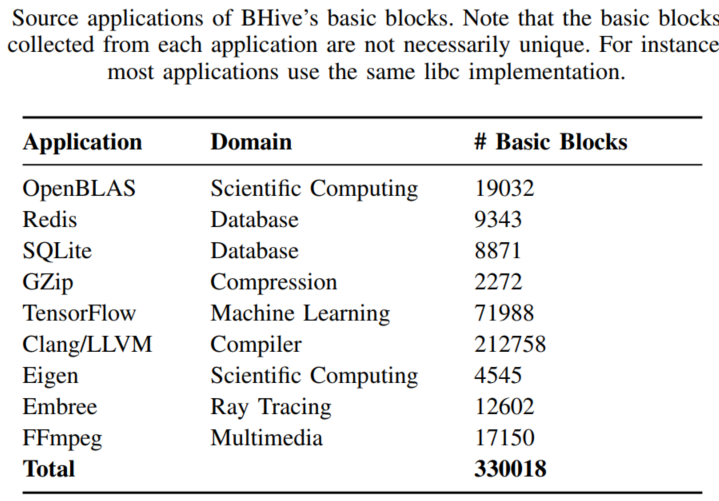

现在已经有超过30万的基本块分析,来源于各种方向的应用,包括数值计算OpenBLAS,数据库SQLite,机器学习TensorFlow,密码学OpenSSL。

这么多的数据产生了一个用于评估performance model的新benchmark。

作者说performance modeling 研究的未来在于与其他先进技术的大规模定量比较

通过把虚拟页面映射到单个物理页面,来合法内存访问同时避免cache miss

有两种model

1. 产生可以详细描述指令何时发射和退休的可解释执行路径的微架构模拟器,附带吞吐量预测。

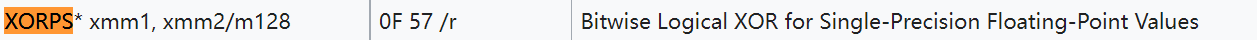

2. 每条指令都有延迟、吞吐量查找表,相当于一个被寄存器分配器使用的额外开销估计器

各种model, 写到另一篇里了

- IACA

- llvm-mca

- OSACA

- Ithemal

- 通过 Agner Fog’s script 测量真实的,有周期,cache miss 等等。https://www.agner.org/optimize/testp.zip

- nanoBench也是。https://github.com/andreas-abel/nanoBench 可以指定processor?和 kernel模式。

- Unrolling

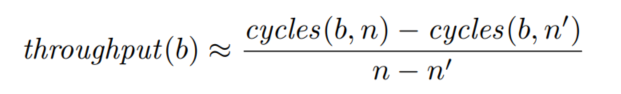

- 测量吞吐量的基本方法就是展开一个基本块的代码多次,然后测重复多次的代码。把展开的基本块latency除以

unroll factor(典型值是100)

- 目的:

- 边缘化前几次warm up的latency值的影响。

- 减少收起数据的开销影响

unroll factor就是循环展开次数。- 局限性是,必须人工给代码块,不能自动profile一堆任意的基本块来系统性验证。???

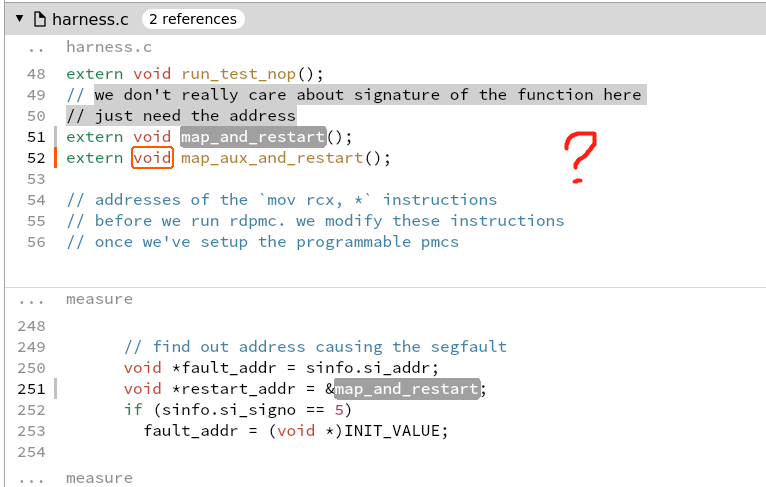

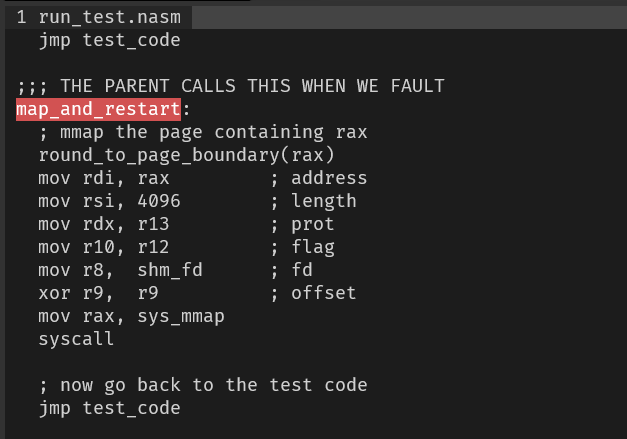

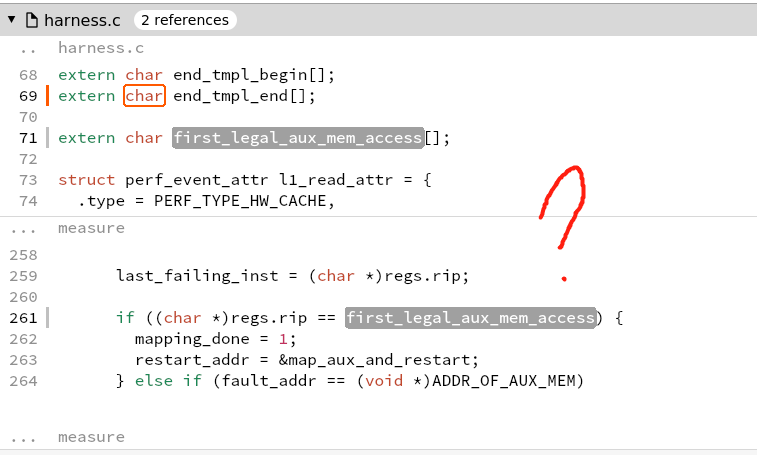

目标是在不需要手动干预的情况下分析任意基本块,以便测量的吞吐量与性能模型通常假定的定义和不变量相对应。关键的挑战是使这些基本块能够在不崩溃的情况下访问任意内存地址。

由于基本块只是正常程序的一部分,导致根本不能单独正常运行。BHive做的事情就是,让他正常运行。

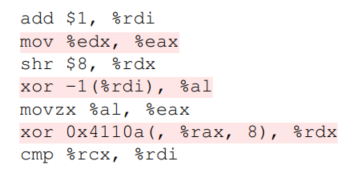

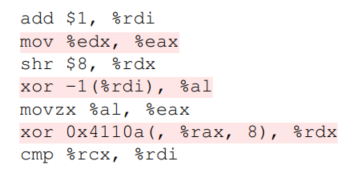

这个代码块只有执行代码分配在

这个代码块只有执行代码分配在0x4110a时,才能正常运行

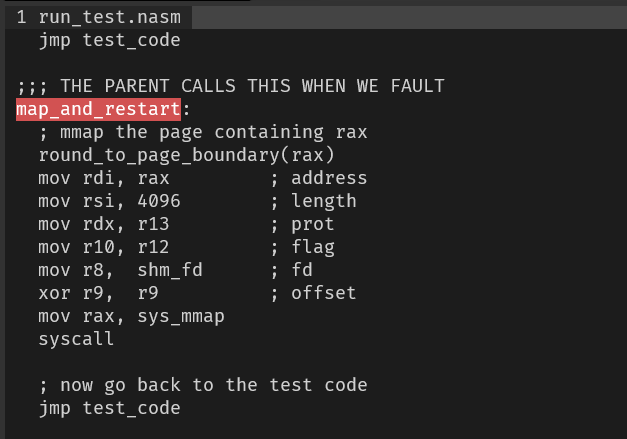

1. Remapping Virtual Pages.

1. 一个基本块的所有虚拟内存页重新映射到一个物理页上,所以全部数据访问都命中L1。这样就可以执行97%的基本块。

2. 步骤

1. 把原本虚拟页全部unmap

1. 这会导致除了包含基本块指令的页之外的全部的连续的内存访问出问题???

2. 在子进程里运行展开的基本块指令。

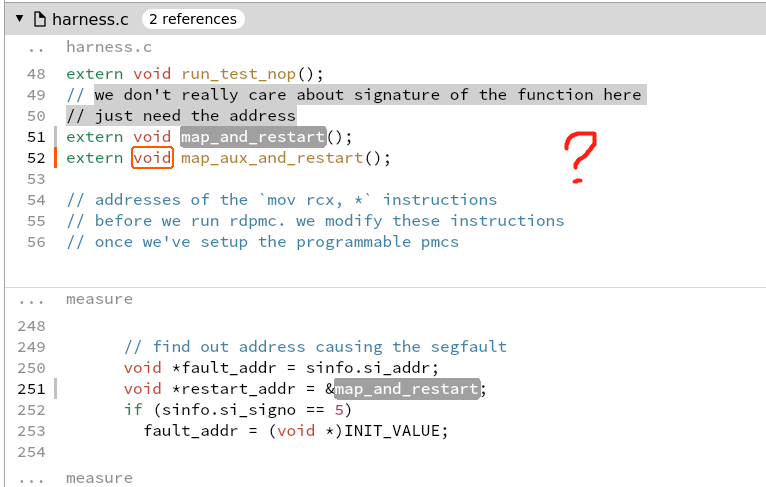

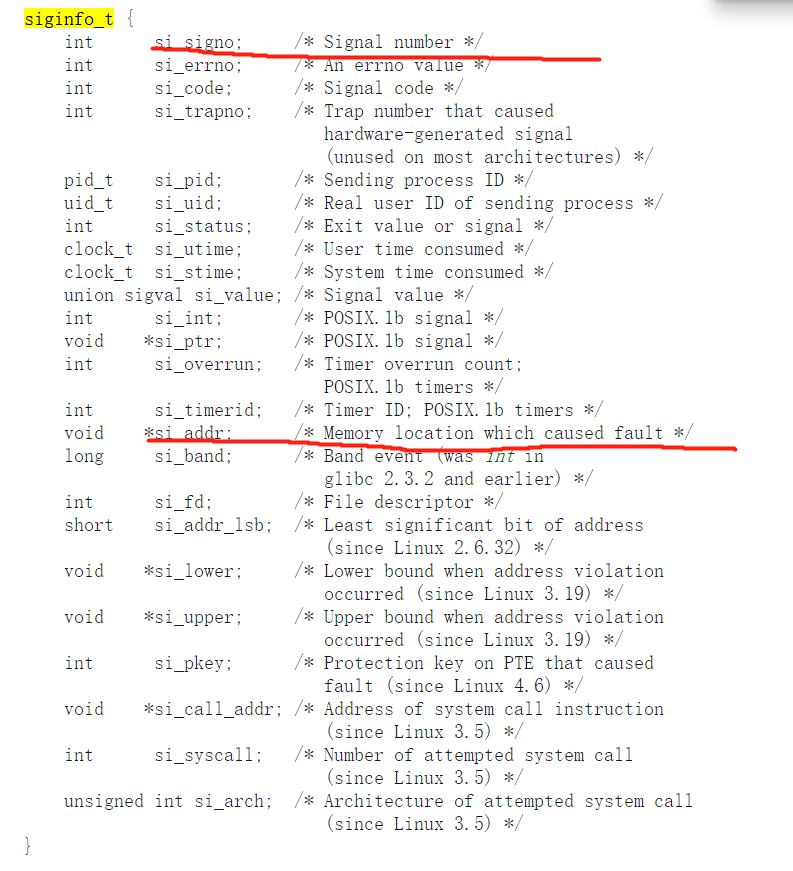

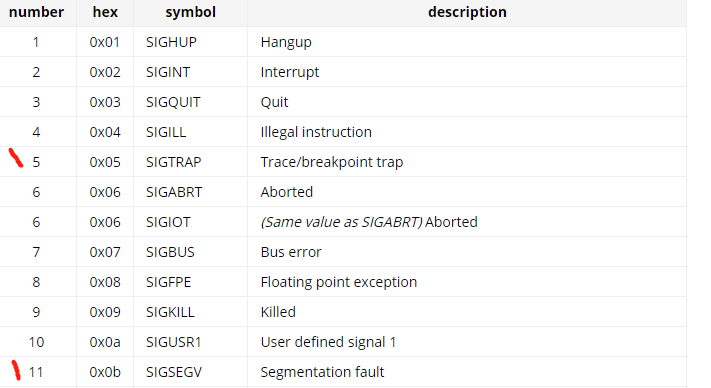

1. 这时对每个unmap的虚拟页的访问都会出错,但是主进程一种监视着。一旦中断就重新映射出错地址,然后重新开始跑。

2. Memory Initialization

1. 初始化一个中等大小0x12345600的物理页,允许都虚拟页都映射

3. Virtual page aliasing

1. 因为不同的虚拟页映射在同一个物理页的同一项导致memory dependences,要等待

2. 剔除6.28%的基本块

3. 可以通过增大物理页,来减小发生的概率。

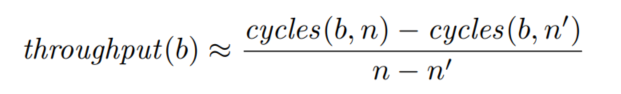

通过重复运行基本块来计算吞吐量

1. Raw Measurement

1. 先从基本块里,产生不会memory crash的可执行部分。

2. unroll factor的选取。It uses 100 and 200 as the unroll factors for basic blocks smaller than 100 bytes; 50 and 100 for basic blocks between 100 bytes and 200 bytes; and finally 16 and 32 for basic blocks larger than 200 bytes

2. Filtering

1. 筛选执行代码满足理想化模型的执行结果,比如命中L1cache

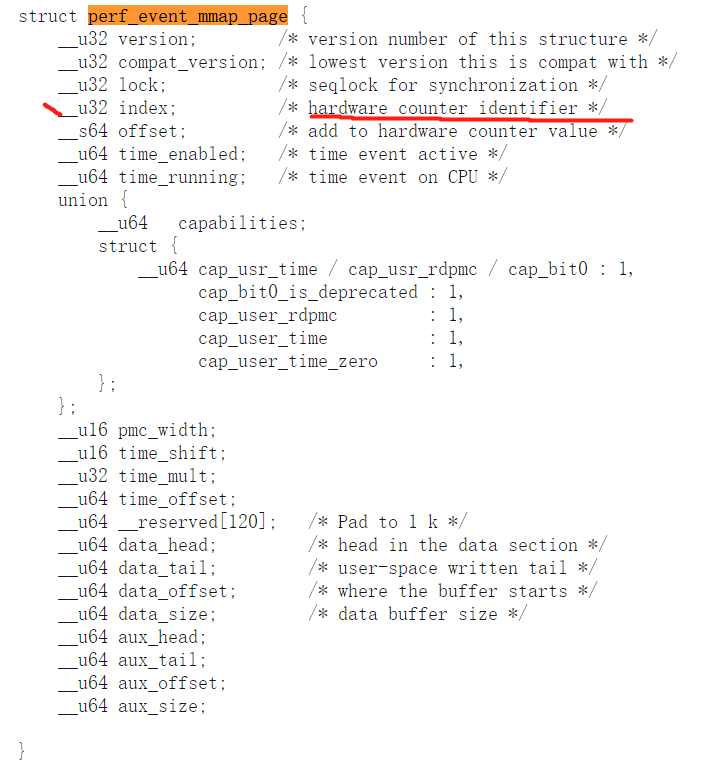

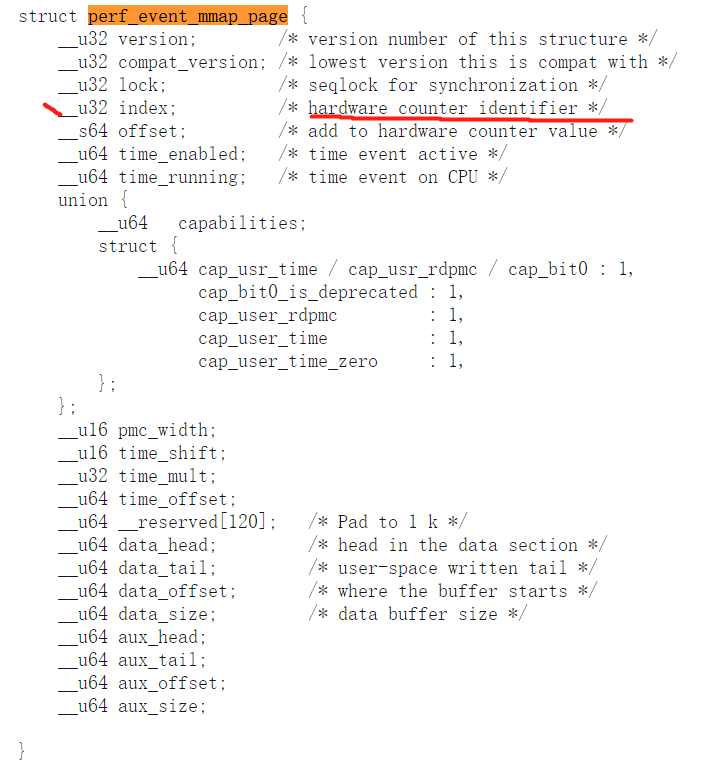

2. L1 Cache Misses

1. 工具可以用硬件计数器监控指令和数据cache misses。拒绝所有cache miss的情况。

3. Unaligned Loads

1. 不连续的访存会很慢,解决方法就是去除所有有不连续的访存的。大约删除了0.18%的基本块

4. Subnormal Floating Point

1. 一些特殊的浮点数计算会比正常的浮点数计算慢20倍,去除了与MXCSR寄存器有关的0.1%的基本块。

2. https://stackoverflow.com/questions/8341395/what-is-a-subnormal-floating-point-number

5. Context Switches

1. 上下文切换(英语:context switch),又称环境切换,电脑术语,是一个存储和重建CPU的状态 (内文),因此令多个进程(process)可以分享单一CPU资源的计算过程。要切换CPU上的进程时,必需先行存储目前进程的状态,再将欲运行的进程之状态读回CPU中。

6. 可接受的评估公式 10%的误差???

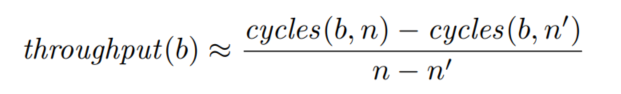

3. Throughput Calculation

1. 如果通过了基本块的筛选,用有记录的最小延迟计算吞吐量 4. Environment Variance

1. 由于环境的影响,导致结果有个稳定的偏移。至少执行5次,展开16次的基本块。取最小的5次作为结果。

4. Environment Variance

1. 由于环境的影响,导致结果有个稳定的偏移。至少执行5次,展开16次的基本块。取最小的5次作为结果。

只要架构满足以下几点要求

1. 有将多个虚拟页面映射到几个物理页面的API。map

multiple virtual pages to a few physical pages

1. without incurring a performance penalty due to unnecessary cache invalidation. We therefore require that the target processor has a physically tagged data cache(VIPT)???

1. we additionally require that the page size is small enough so the indexing bits are

not affected by address translation.

1. detecting cache misses,

2. and detecting or disabling floating-point underflow.

应用的选择

- 尽可能还原现实生活的各个方面,

- 而且是用户的典型用法。

- Clang/LLVM (compiler), Redis (inmemory database), SQLite (database), and Gzip 是用高级语言C或者C++编写的,算法和数据结构有复杂的设计。

- OpenSSL (cryptography), OpenBLAS , Eigen (scientific computing),TensorFlow (machine learning) 代表的是核心循环是手动汇编优化过的高性能库。

- 其中Embree是 用Intel ispc (a data-parallel language)编写的。

We compiled all applications with the highest optimization settings defined by their build systems. 如果可以用上了AVX2。

使用DynamoRIO动态分析来提炼基本块。可以实现在运行时记录每个运行的基本块。我们采用动态分析,而不是静态反汇编。因为静态反汇编无法区别padding bytes from instructions。???

应用的例子除了FFmpeg and Gzip都是选择的官方的benchmark。

Eigen 采用的是 two sparse linear algebra workloads: sparse matrix-matrix multiplication (SpMM) and sparse matrix-vector multiplication (SpMV).

一些基本块比其他的更难建模,???(建什么模,VI-B说明了什么)有内存依赖的基本块预测错误率更高。

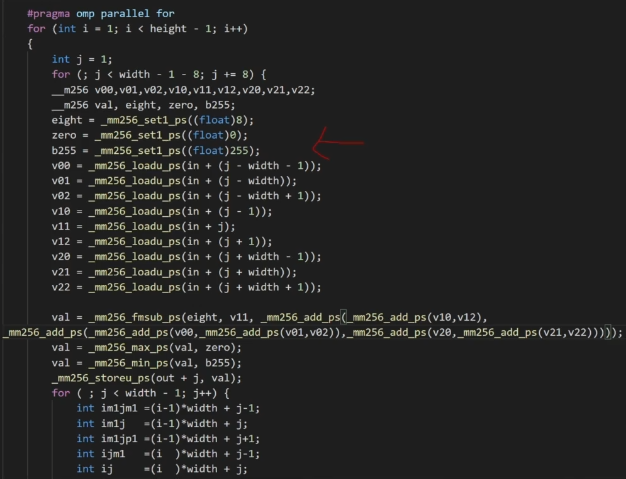

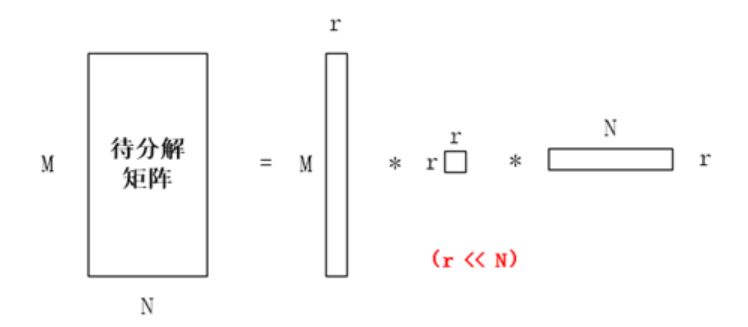

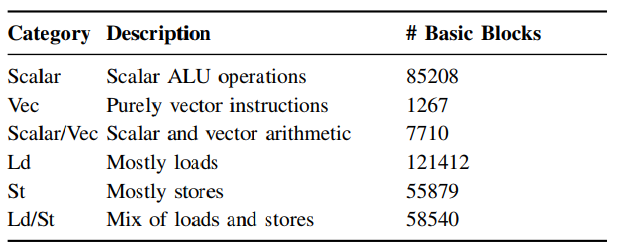

采用了一种技术???(是应用在提取上) 基于处理器的使用聚类基本块。

这个技术有助于性能模型的设计和使用者更细粒度了解performance model,让他们能集中以后新添加的资源在有困难的那一类基本块。

- Methodology

- 具体方法

- 找到每个基本块的硬件使用率的表示 port-mapping representation

- 根据其聚类

- 对每条指令结合port使用

- 运用 Abel and Reineke A. Abel and J. Reineke, “uops.info: Characterizing latency, throughput, and port usage of instructions on intel microarchitectures,” in ASPLOS, 2019的结果 ???

- 例如???

xor %rax, %rbx in Haswell is {p0156 → 1}

- 使用Latent Dirichlet Allocation (LDA)来构建topic model 模型(python 训练模型)

- 在语言处理上的应用是基于统计词频

- 在实际运用的时候,微指令操作会根据使用的port而有小不同。

- topics是分类的类别,6类

- documents是基本块

- α = 1/6 and β = 1/13.

- 为了推断每个微指令操作所属的类别,我们使用了SciKit Learn transform对于LDA的随机变化推断的默认实现

- 计算每个基本块的最有可能的类别作为其分类结果

- Results

- LDA将结果聚类后,根据基本块的内容,手动进行注名以及说明

- example

- 根据运行时频率确定其权重, 基于sample-based profiler??? (A portable sampling-based profiler for java virtual machines,)确定。

- 高性能的库如预期一样,向量化的基本块占比较多。

- 其余的无向量化的较多。OpenSSL and Gzip有许多位操作的。

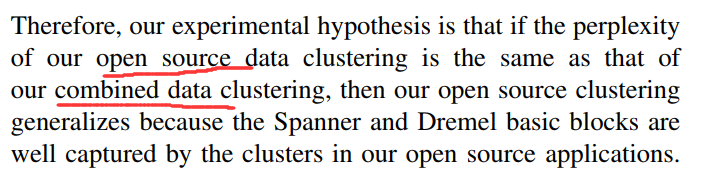

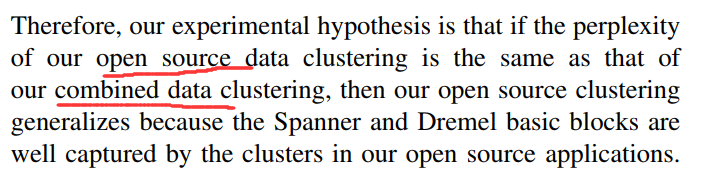

- Case Study on Data-Center Applications

- 目的:作为测试例子,看这个聚类方法能不能找得到隐藏的热点、工作负载

- Methodology

- 第一步:首先将其基本块分成之前的几类,还是使用LDA

- 第二步:分类结果标注

- 第三步:比较聚类结果的perplexity值???

- ???有没有结合google的应用

- Results

- 添加新应用后,该值只是略微增长。说明模型的代表性好。???

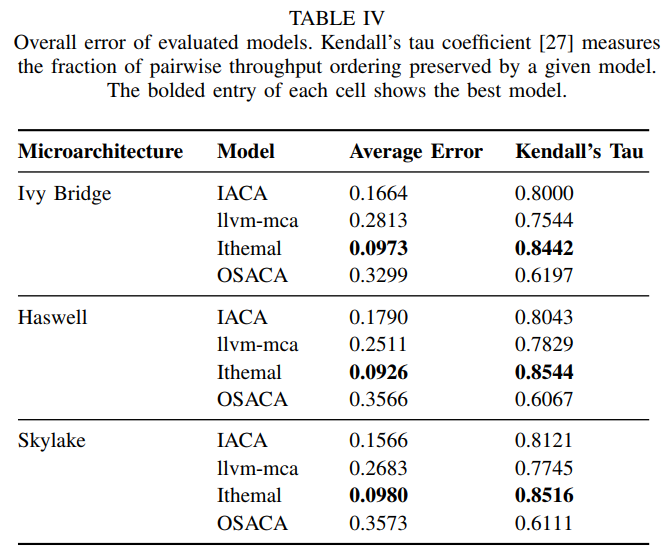

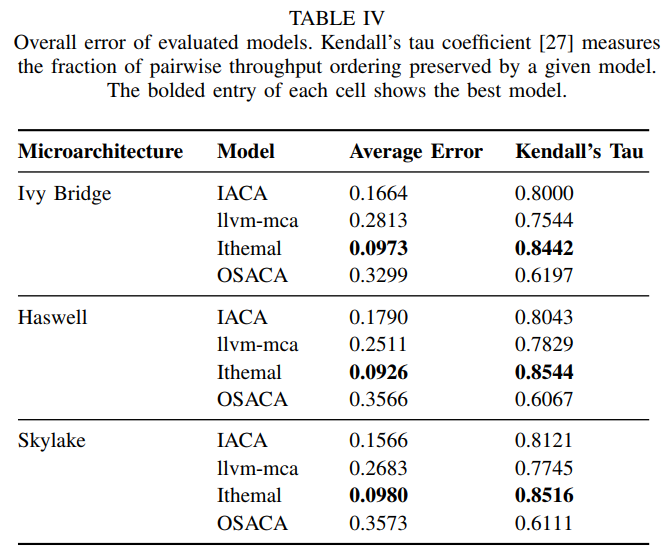

在3种Intel架构上验证4种已有的性能模型

1. Methodology

1. 说明各个测试软件的版本。

2. Dataset

1. basic block dataset discussed in Section IV

3. Platform

1. balabala 3种架构的 Intel cpus

4. Evaluation Metrics

1. 测量吞吐量t和预测吞吐量t'$\(err(t,t')=|\frac{t-t'}{t}|\)$

2. 不以预测精度,而是以预测结果的相对关系为评分标准。

5. 额外能评估每个模型如何保持基本块吞吐量的顺序。使用Kendall’s tau系数(越大效果越好),而不是相对误差。测量的原因是使用者可能关心的不是绝对的数值精度,而是相对关系的准确率。比如优化软件的时候关心的不是具体耗时,而是哪个优化策略耗时更短。

2. Results

1.  2. IACA 第二好的,在向量化类模拟的最好

3. llvm-mca 最差的,尤其是和loads有关时。

4. Ithemal 除了向量基本块都是最好的。在memory dependence (Ld/St)尤其好,但是向量基本块不好,可能与训练集没有向量基本块有关。

5. OSACA 第三。由于还在开发中,使用还遇到5个bug。在遇到一些不认识的指令的时候,会直接按照nops空指令处理。

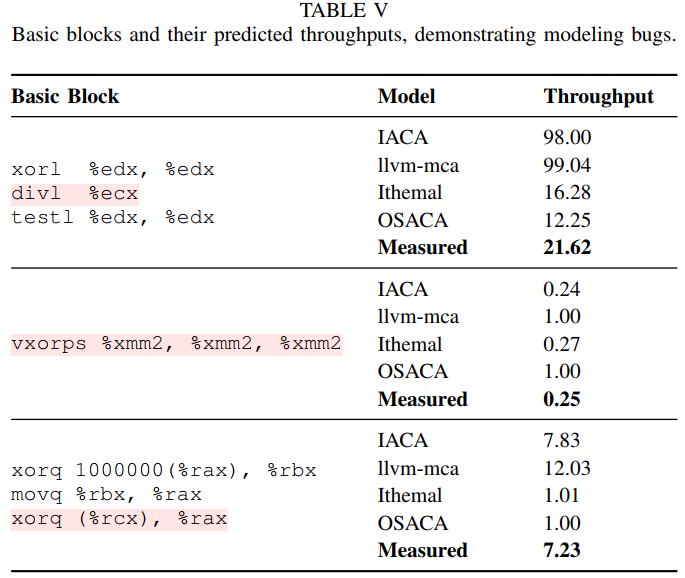

3. Examples of Modeling Bugs

2. IACA 第二好的,在向量化类模拟的最好

3. llvm-mca 最差的,尤其是和loads有关时。

4. Ithemal 除了向量基本块都是最好的。在memory dependence (Ld/St)尤其好,但是向量基本块不好,可能与训练集没有向量基本块有关。

5. OSACA 第三。由于还在开发中,使用还遇到5个bug。在遇到一些不认识的指令的时候,会直接按照nops空指令处理。

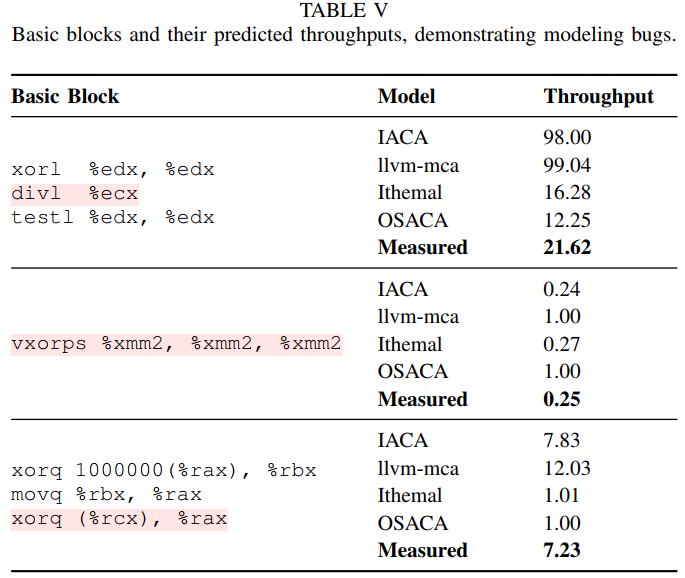

3. Examples of Modeling Bugs 1. 最后一个例子是由于模型错误调度微指令导致的

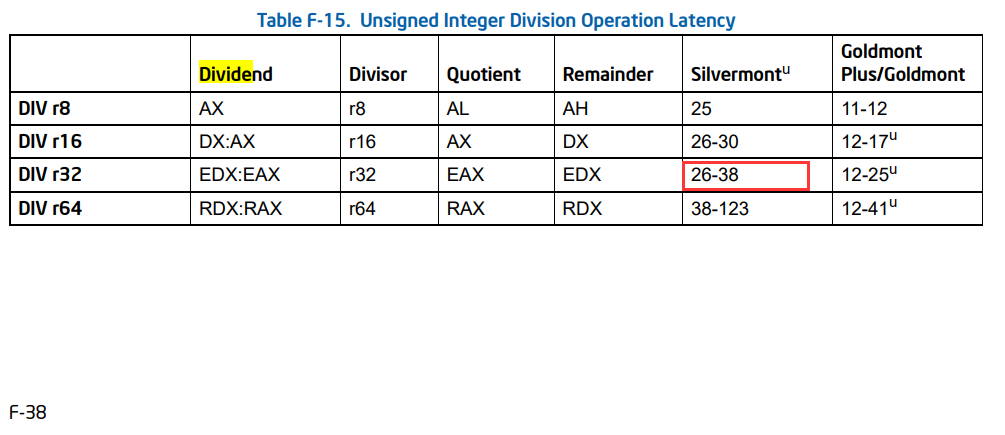

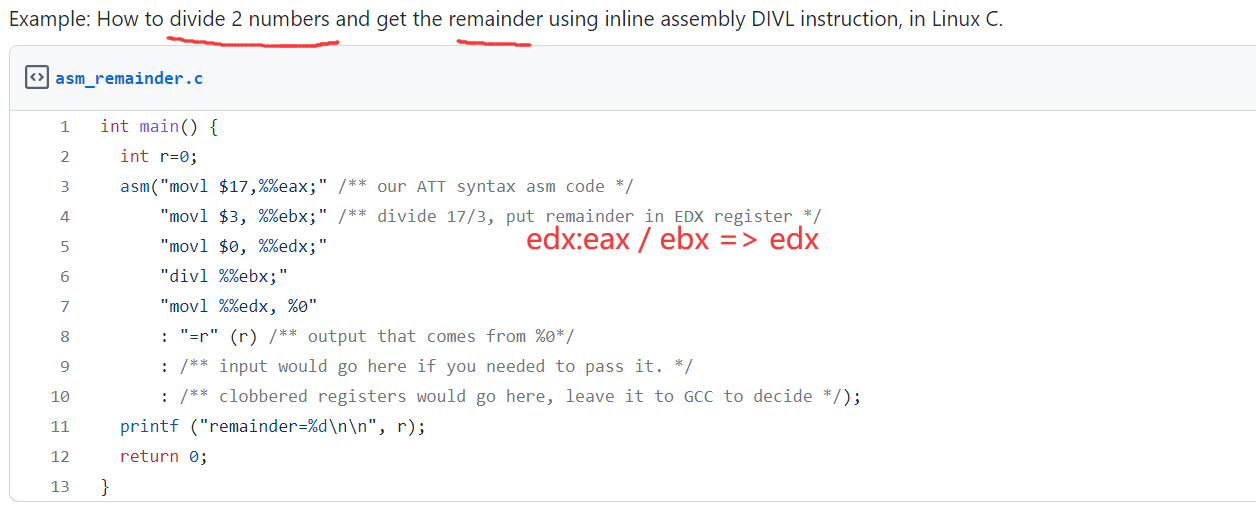

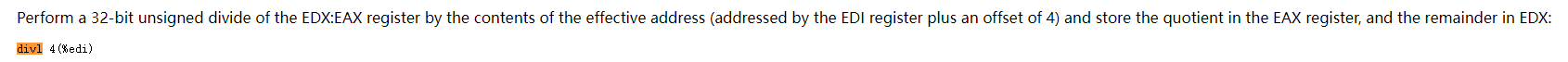

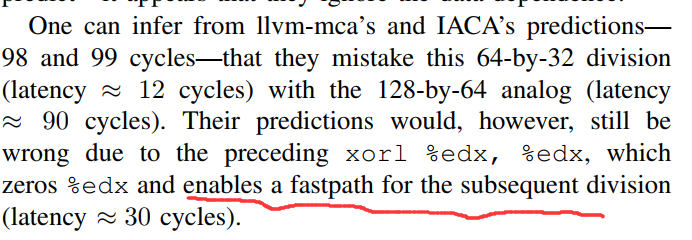

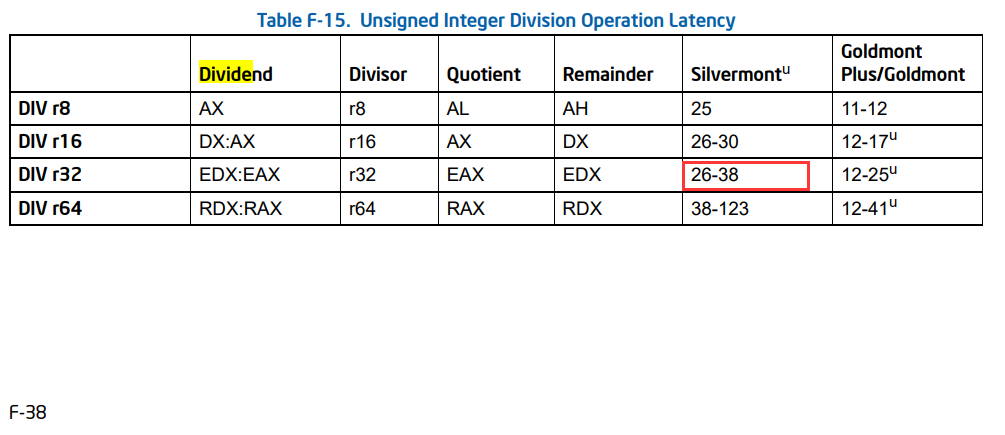

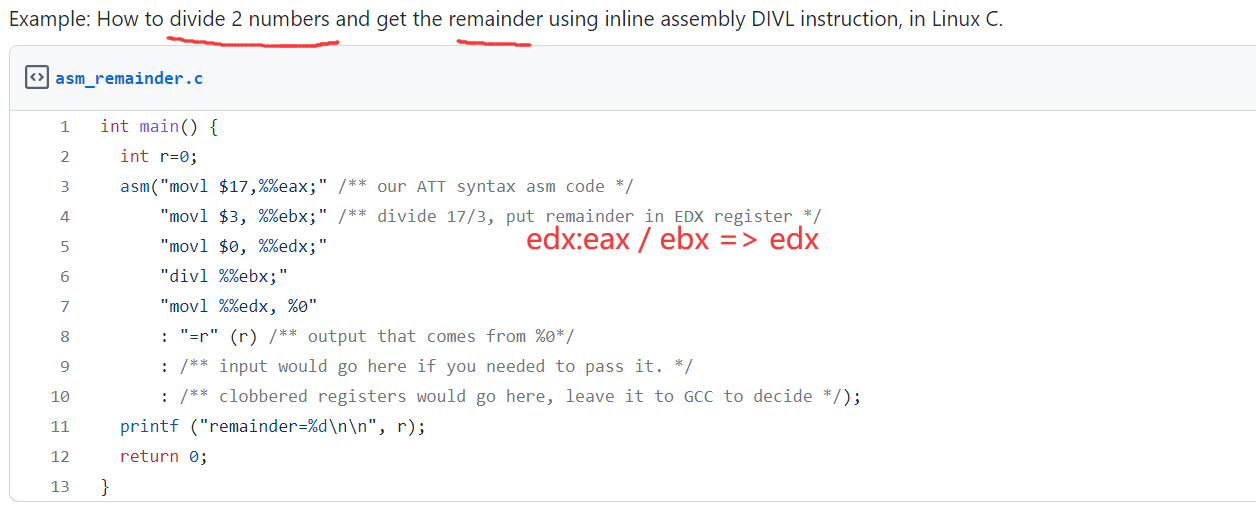

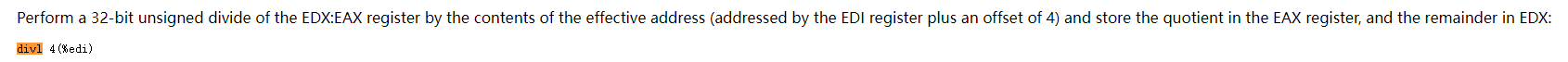

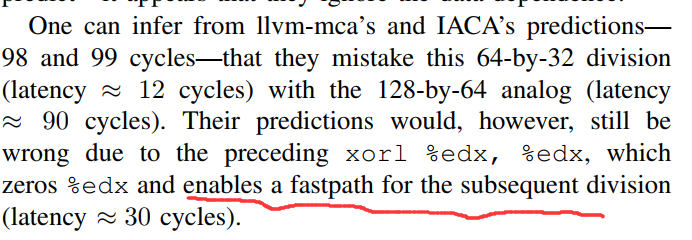

2. Modeling bug due to unsigned division

1. 例子是 a 64-bit by 32-bit unsigned division.

1. 最后一个例子是由于模型错误调度微指令导致的

2. Modeling bug due to unsigned division

1. 例子是 a 64-bit by 32-bit unsigned division.

2. ???

2. ??? 3. Modeling bug due to zero-idioms

1.

3. Modeling bug due to zero-idioms

1.  2. 对这种结果固定的特殊指令的快速处理。

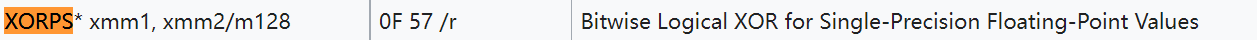

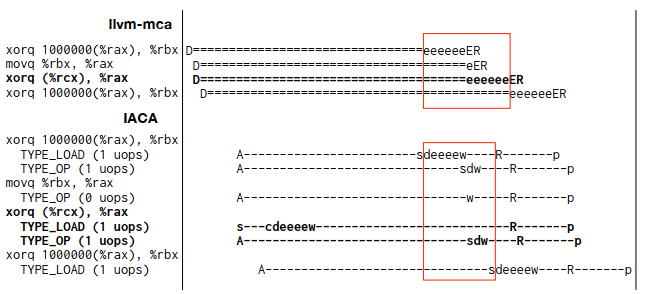

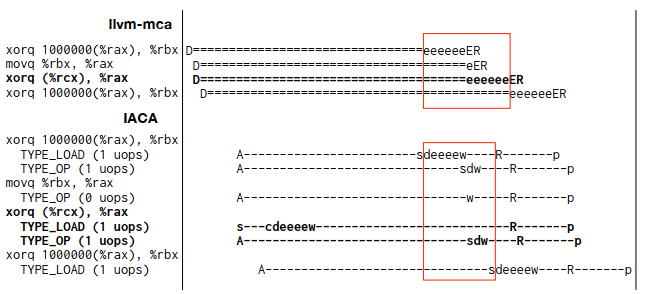

4. Modeling bug due to mis-scheduling

1. 对于数据依赖,上下指令的寄存器有写后读。

2. Ithemal’s and OSACA忽略了该依赖

3.

2. 对这种结果固定的特殊指令的快速处理。

4. Modeling bug due to mis-scheduling

1. 对于数据依赖,上下指令的寄存器有写后读。

2. Ithemal’s and OSACA忽略了该依赖

3.  4. llvm-mca 没有注意到(%rcx)是memory,没有依赖可以提前发射。

4. llvm-mca 没有注意到(%rcx)是memory,没有依赖可以提前发射。

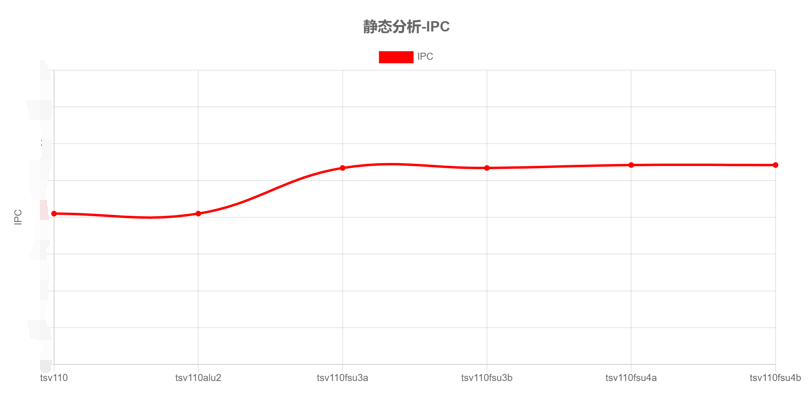

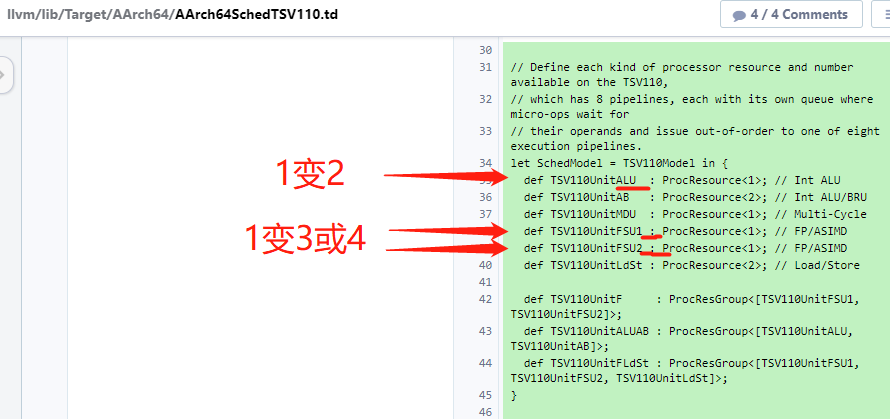

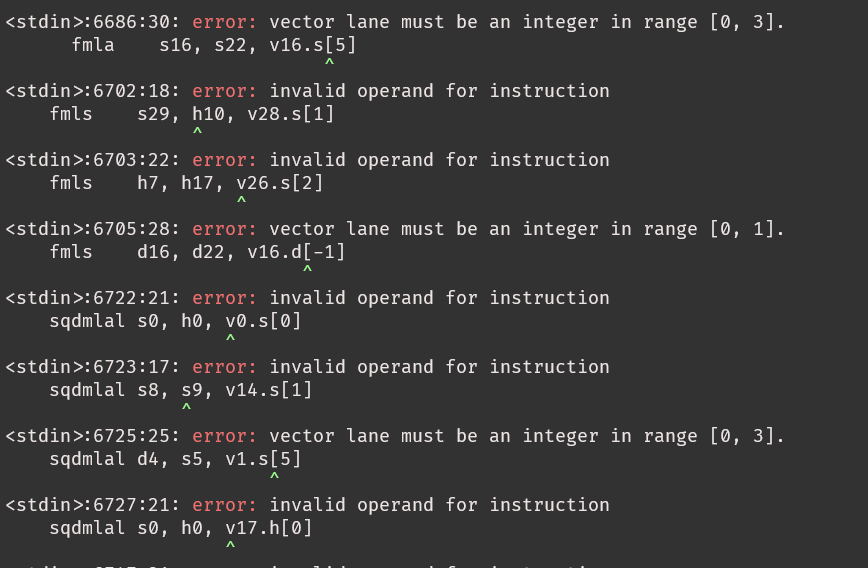

现有的静态分析器对内存依赖和向量化块的建模还有困难。

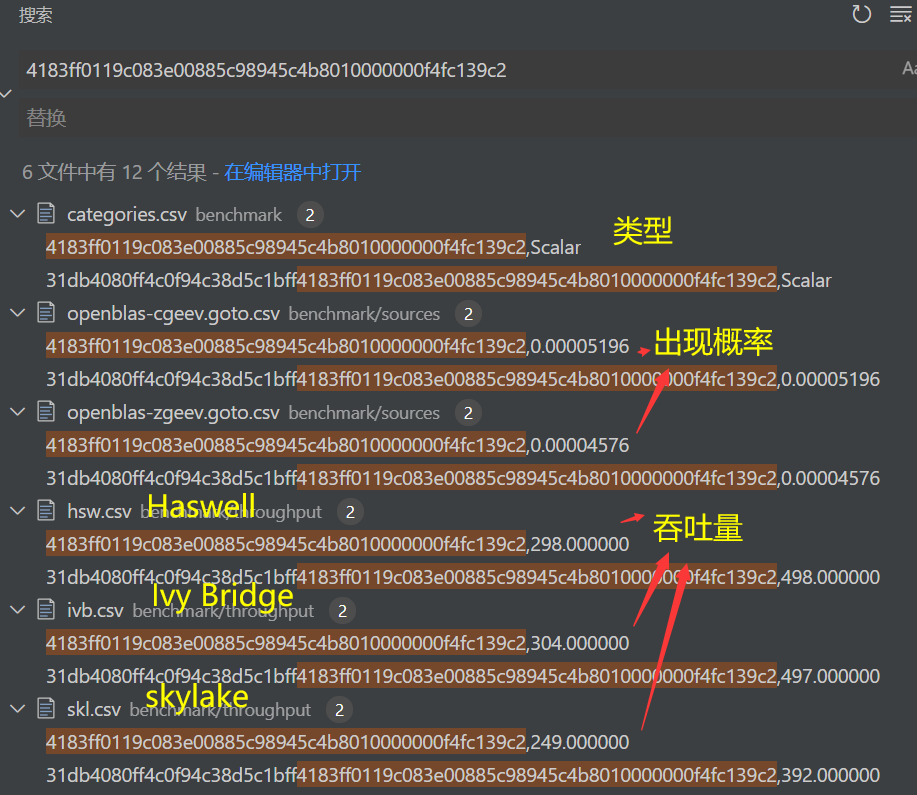

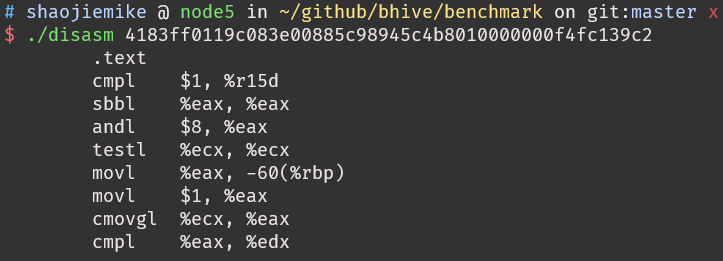

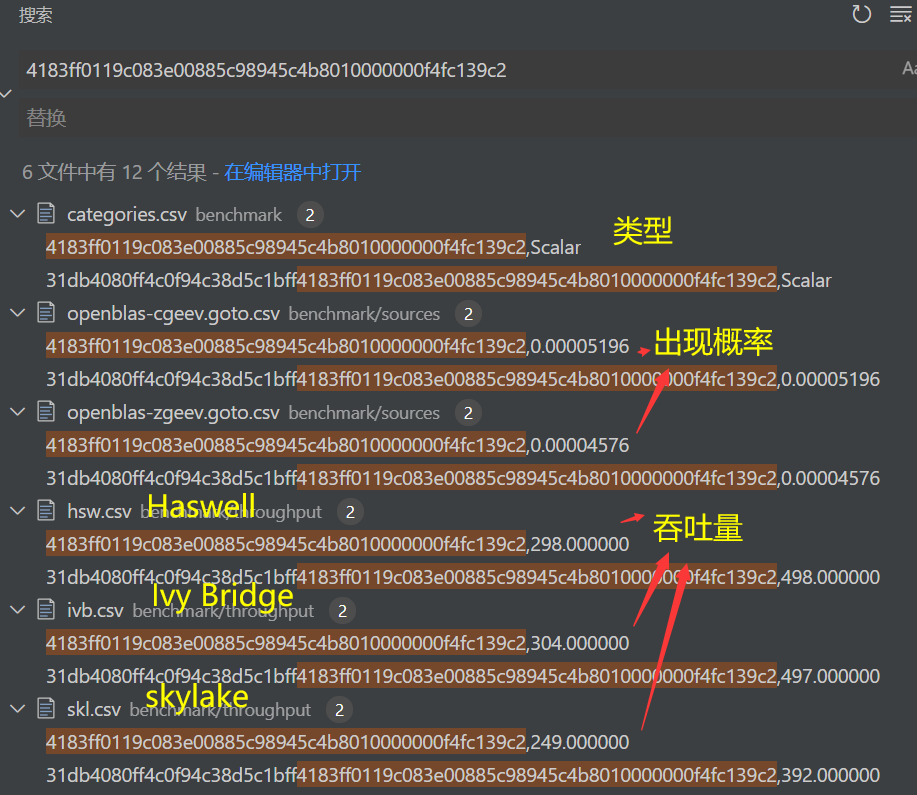

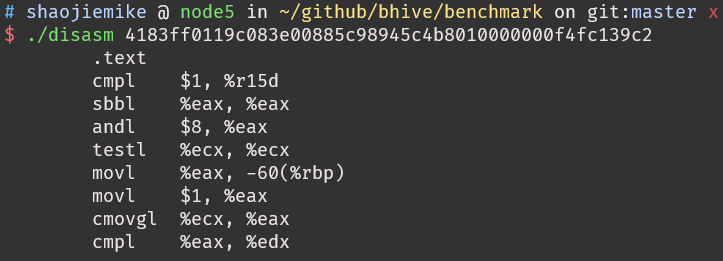

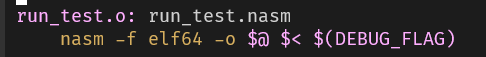

benchmark/sources下是各种软件的各个部分的16进制基本代码块和其出现概率,用csv格式(逗号分隔值 (Comma-separated values))存储benchmark/throughput是在各种架构下的各基本块的测量吞吐量,单位cycles per hundred-iterations.

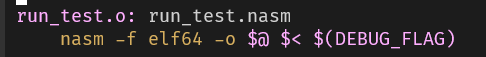

benchmark/disasm可以把16进制代码通过nasm变成汇编,

timing-harness

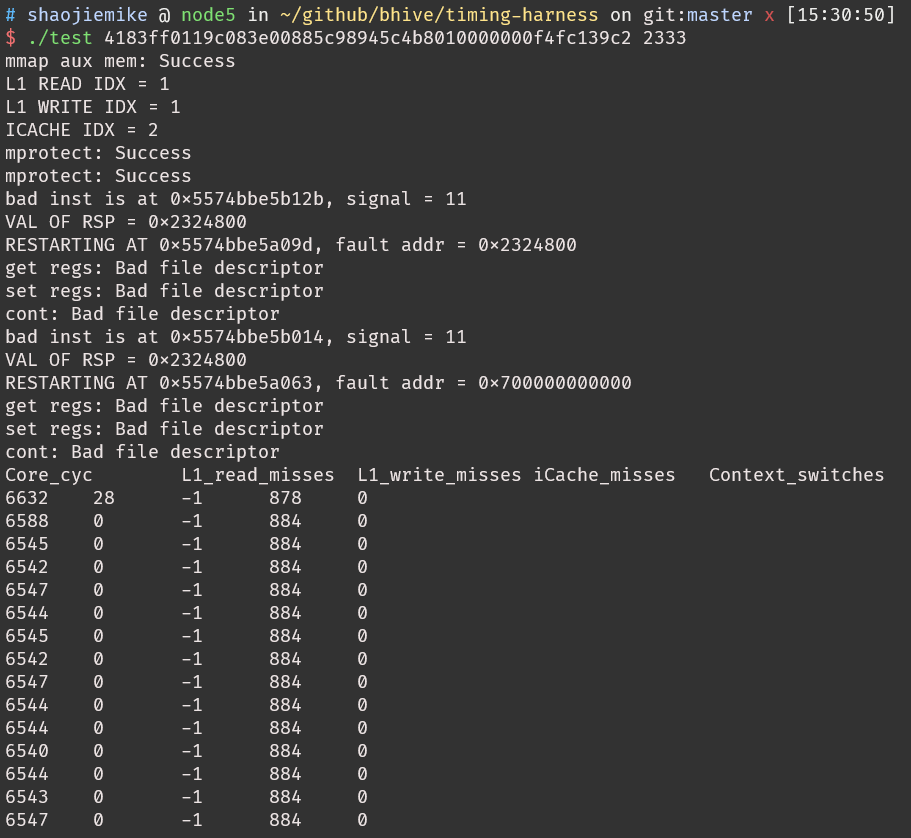

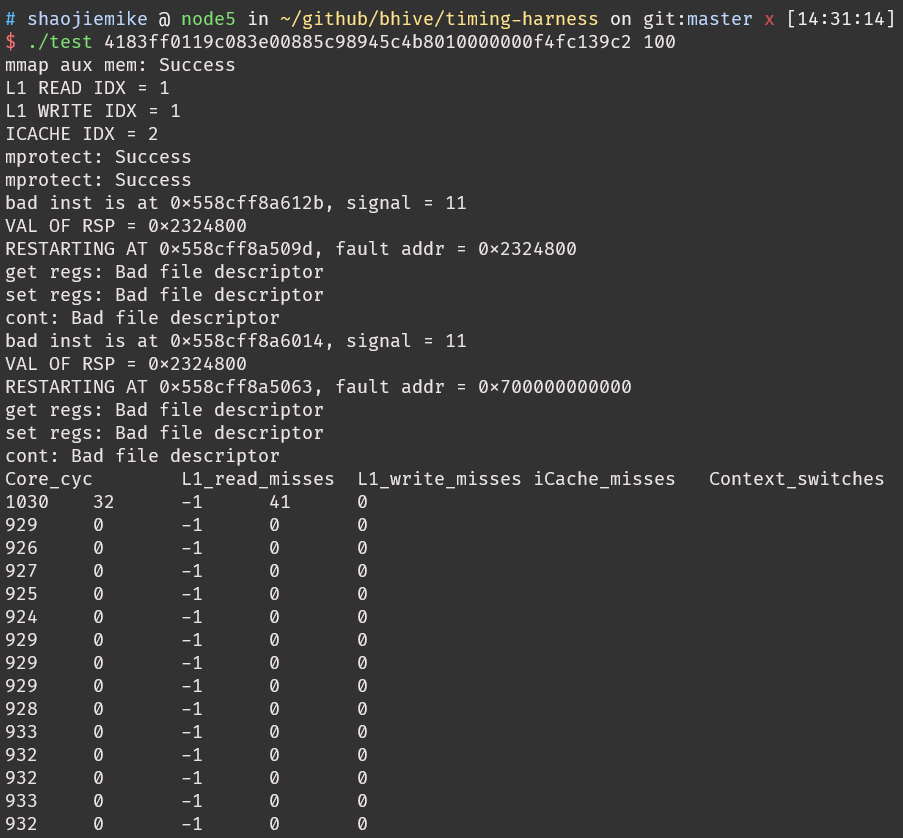

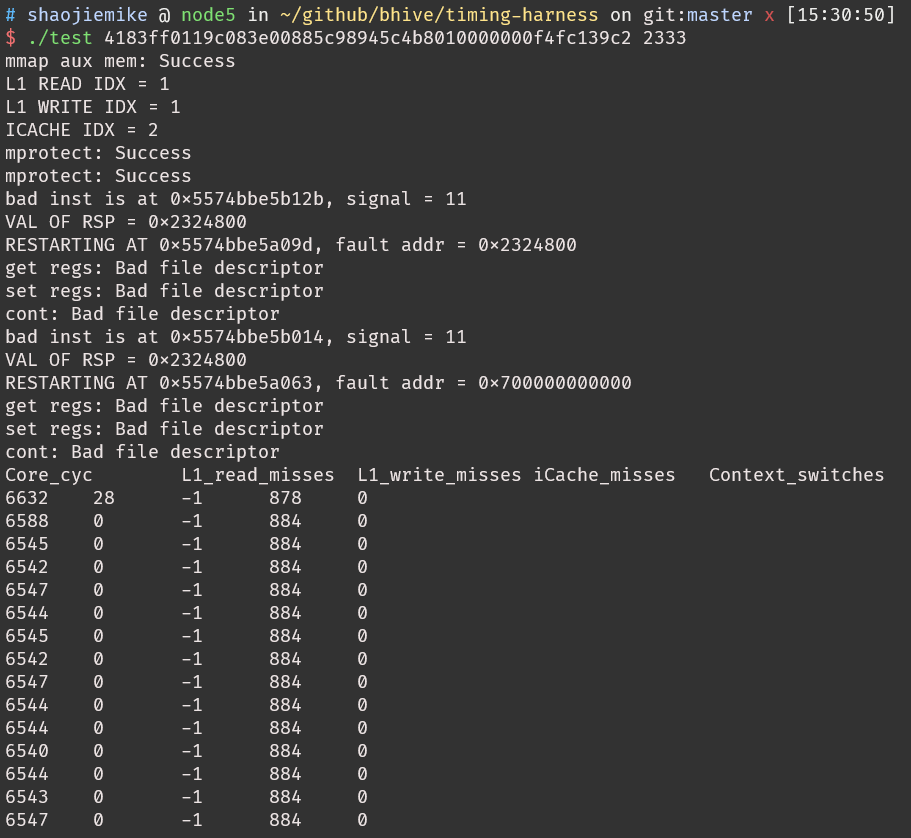

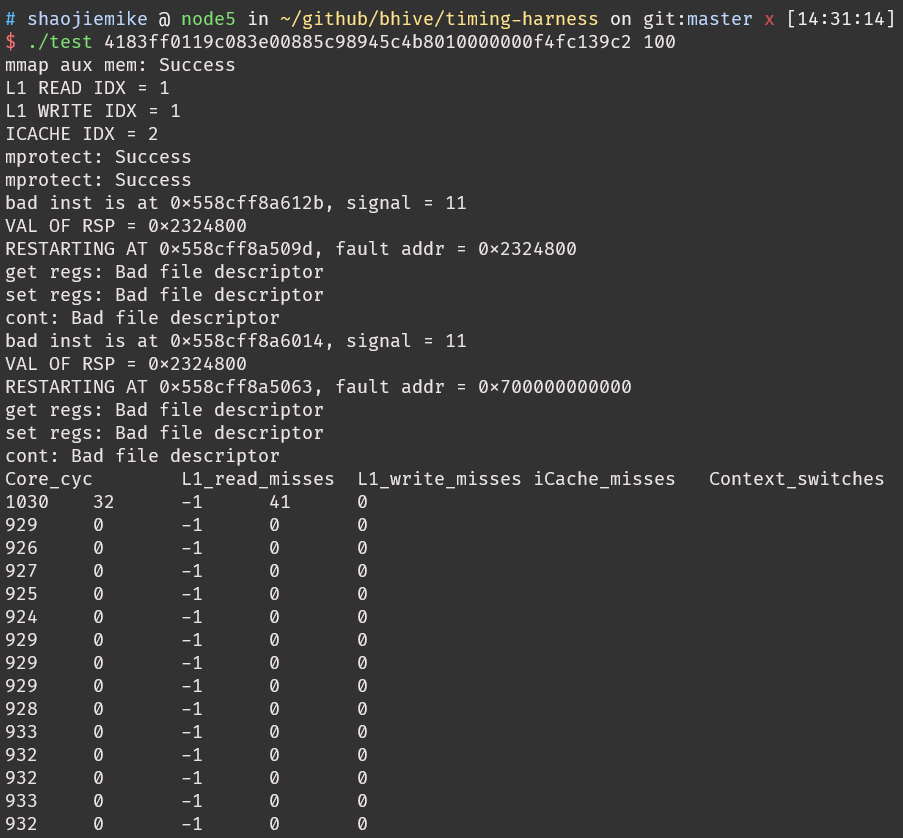

吞吐量的计算(猜的)Skylake microarchitecture$\(\frac{6632-1030}{2333-100}*100=250.8 (cyc/hundred\ iters)\)$

吞吐量的计算(猜的)Skylake microarchitecture$\(\frac{6632-1030}{2333-100}*100=250.8 (cyc/hundred\ iters)\)$

uops 的文章, Accurate Throughput Prediction of Basic Blocks on Recent Intel Microarchitectures

4.2 Extending BHive

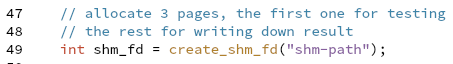

- 读入16进制代码和循环次数

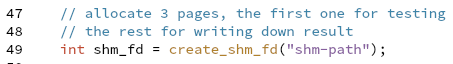

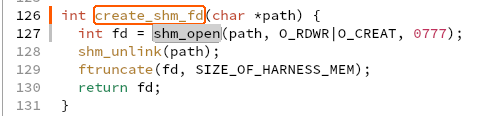

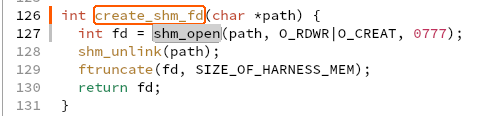

hhex2bin转换为二进制create_shm_fd

-

shm_open, shm_unlinkcreates and opens a new, or opens or unlink an existing, POSIX shared memory object. O_RDWR Open the object for read-write access.O_CREAT the shared memory object if it does not exist. 777是类似文件读写执行组权限的东西 On success, shm_open() returns a file descriptor (a nonnegative integer)

-

POSIX可移植操作系统接口The Portable Operating System Interface 是IEEE为要在各种UNIX操作系统上运行软件,而定义API的一系列互相关联的标准的总称。

ftruncate — truncate截短 a file to a specified length-

measure开始测量- int fds[2] ???

pipe用于创建pipe,用来进程间通信的单向数据通路,传入变量用来返回引用自pipe末端的文件描述符file descriptors。第一个指向the read end of the pipe,第二个指向the write end of the pipemmap(void *addr, size_t length, int prot, int flags,int fd, off_t offset); munmap(void *addr, size_t length);- map or unmap files or devices into memory 在调用进程的虚拟地址空间里create a new mapping.- fork()产生子进程

- fork()原理详解

- 复制之前的一模一样。

- fork() returns a zero to the newly created child process.

- fork() returns a positive value, the process ID of the child process, to the parent.

- 父进程

-

- 为什么声明一个偏移地址指针???

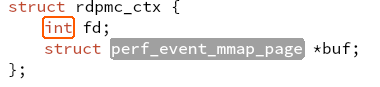

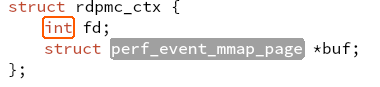

- struct pmc_counters 由5个uint64_t组成。 uint64 will always take 8 bytes。一个结构体40bytes

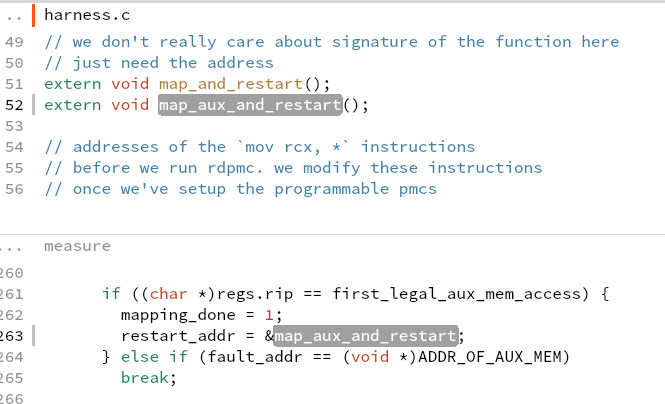

attach_to_child(pid, fds[1]); pid是子进程pid

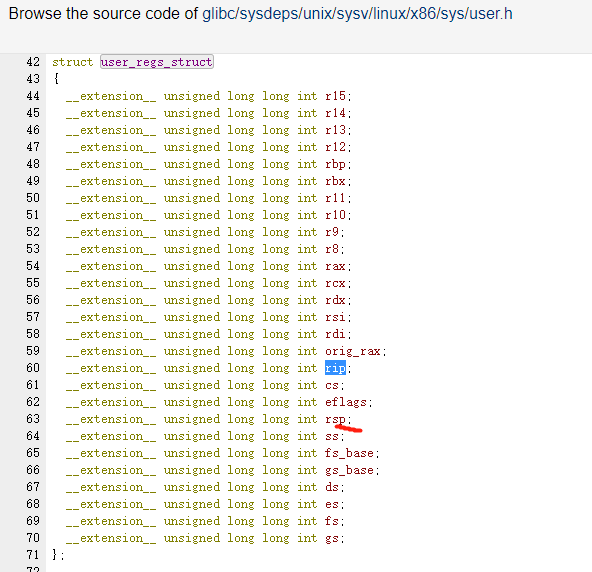

ptrace(enum __ptrace_request request, pid_t pid,void *addr, void *data) - process trace 提供一种进程tracer跟踪控制另一个进程tracee的方法,可以修改被控制者的memory and registers.PTRACE_SEIZE Attach to the process specified in pid, making it a tracee of the calling process. Unlike PTRACE_ATTACH, PTRACE_SEIZE does not stop the process- 子进程从fds[0]里读到x里,父进程把x的值写入 fds[1] ???

- check Performance Monitoring Counters (PMCs) supports

rdpmc_open_attr initialize a raw ring 3 ReaDable PerforMance Counter

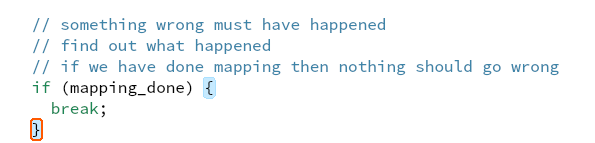

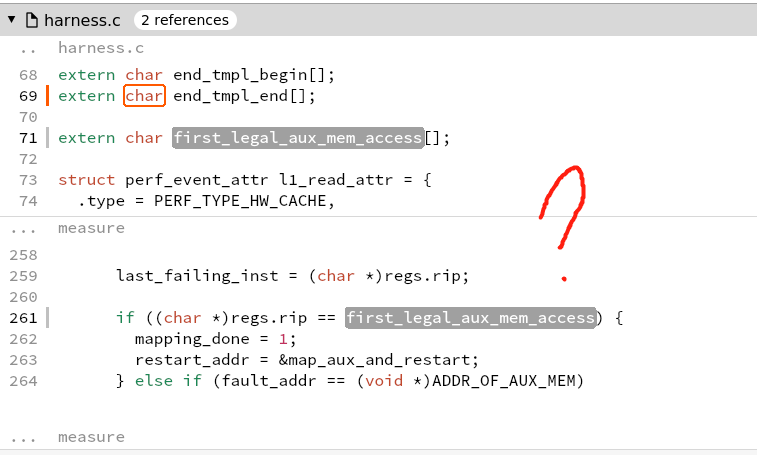

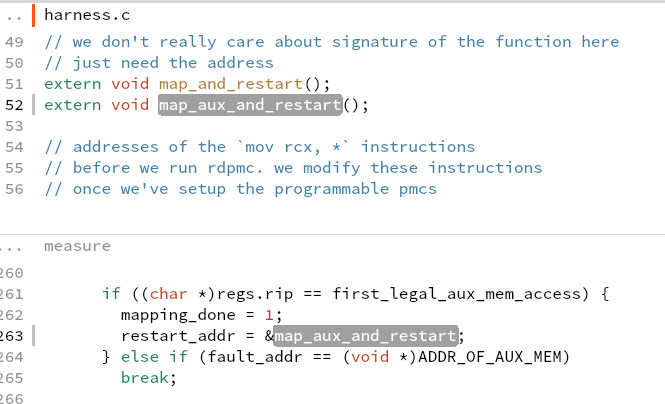

- last_failing_inst 和 mapping_done

- To kill child

-

wait挂起当前线程,直到有一个children结束,返回其PIDWIFEXITEDWait_IF_EXITED 判断是否正常结束

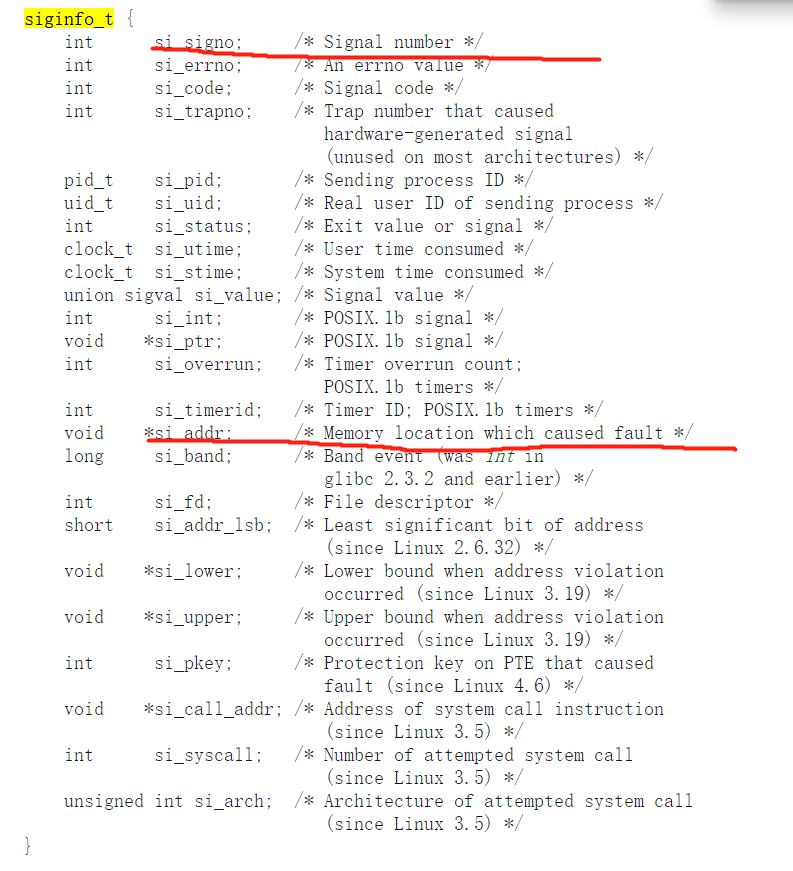

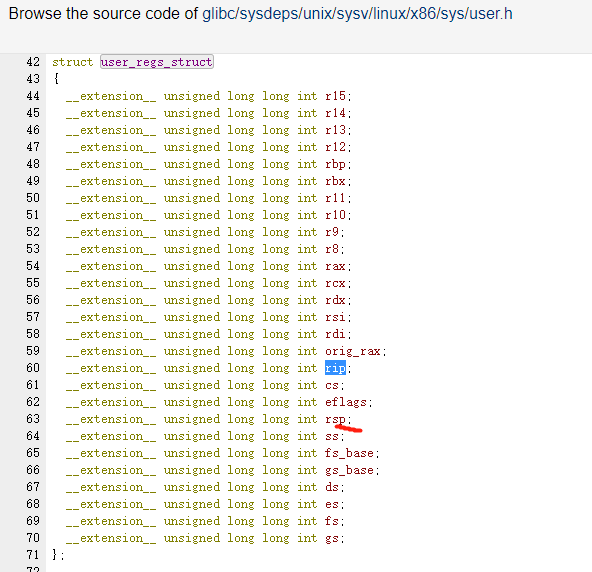

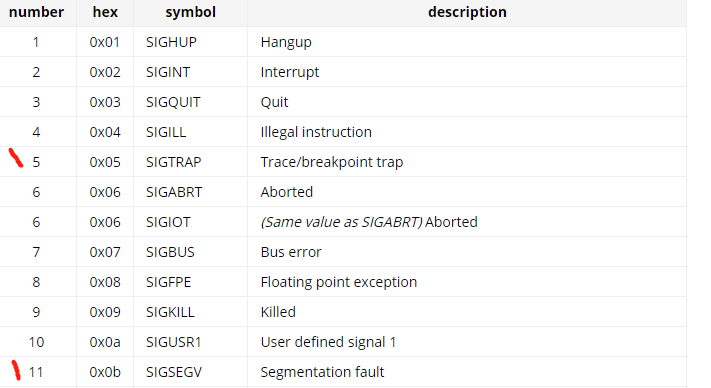

- 如果错误打印出错信号(eg.11)指令指针寄存器RIP,指针寄存器RSP

- 函数是用汇编写的就离谱

what is aux mem?

what is aux mem?

- 修改出错地方的寄存器,重新运行

PTRACE_CONT Restart the stopped tracee process

- 最多执行MAX_FAULTS次

- 最后父进程杀死子进程

- 子进程

- 父进程测试是否支持PMCs,子进程使用

- harness.c :277

https://www.cnblogs.com/from-zero/p/13750852.html

暂无

- time 怎么算的the latency of the basic block?为什么打印15个呢?

- 还有中间的错误是怎么回事?

- 论文里的误差怎么算的?

- BHive整合了几个软件(整合了什么呢),应该是真实测量了得出真实吞吐量?还是也是模拟的?

- 和uops比怎么样

- 哪个数据是准确的,是BHive模拟的,还是真实测量的。

- 通过 Agner Fog’s script 测量真实的,有周期,cache miss 等等。https://www.agner.org/optimize/testp.zip

- nanoBench也是。https://github.com/andreas-abel/nanoBench 可以指定processor?和 kernel模式。

- 局限性是,必须人工给代码块,不能自动profile一堆任意的基本块来系统性验证。???

- BHvie的代码实现,移植到鲲鹏,然后根据PMU调准。

问题是x86的二进制或者汇编不能变成aarm64的二进制或者汇编。

https://github.com/ithemal/bhive

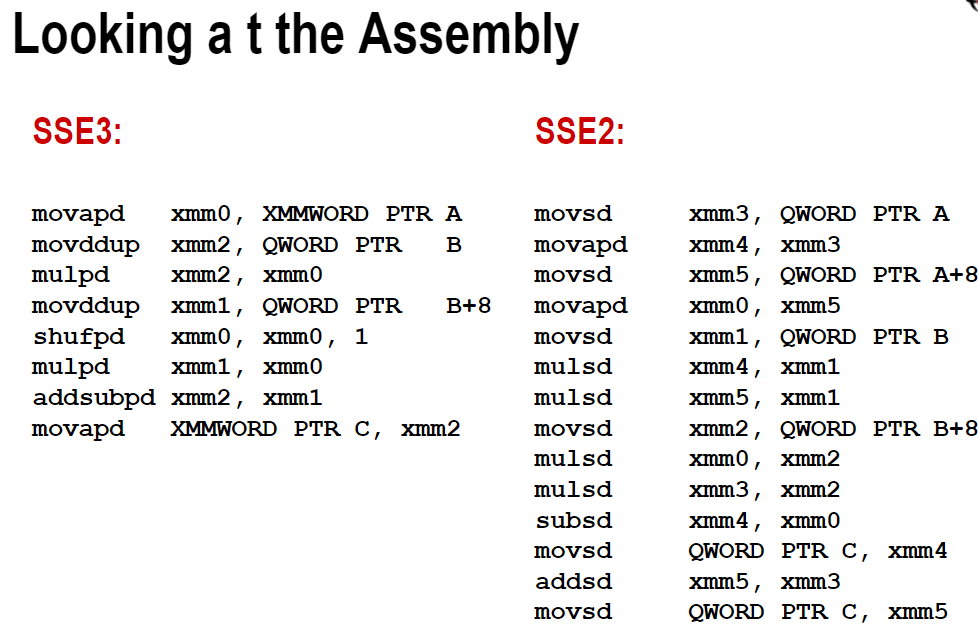

1. SSE2则进一步支持双精度浮点数,由于寄存器长度没有变长,所以只能支持2个双精度浮点计算或是4个单精度浮点计算.另外,它在这组寄存器上实现了整型计算,从而代替了MMX.

2. SSE3支持一些更加复杂的算术计算.

3. SSE4增加了更多指令,并且在数据搬移上下了一番工夫,支持不对齐的数据搬移,增加了super shuffle引擎.

4. 由于2007年8月,AMD抢先宣布了SSE5指令集。之后Intel将新出的叫做AVX指令集。由于SSE5和AVX指令集功能类似,并且AVX包含更多的优秀特性,因此AMD决定支持AVX指令集

1. SSE2则进一步支持双精度浮点数,由于寄存器长度没有变长,所以只能支持2个双精度浮点计算或是4个单精度浮点计算.另外,它在这组寄存器上实现了整型计算,从而代替了MMX.

2. SSE3支持一些更加复杂的算术计算.

3. SSE4增加了更多指令,并且在数据搬移上下了一番工夫,支持不对齐的数据搬移,增加了super shuffle引擎.

4. 由于2007年8月,AMD抢先宣布了SSE5指令集。之后Intel将新出的叫做AVX指令集。由于SSE5和AVX指令集功能类似,并且AVX包含更多的优秀特性,因此AMD决定支持AVX指令集

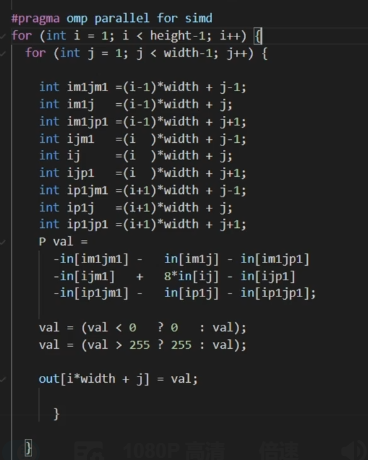

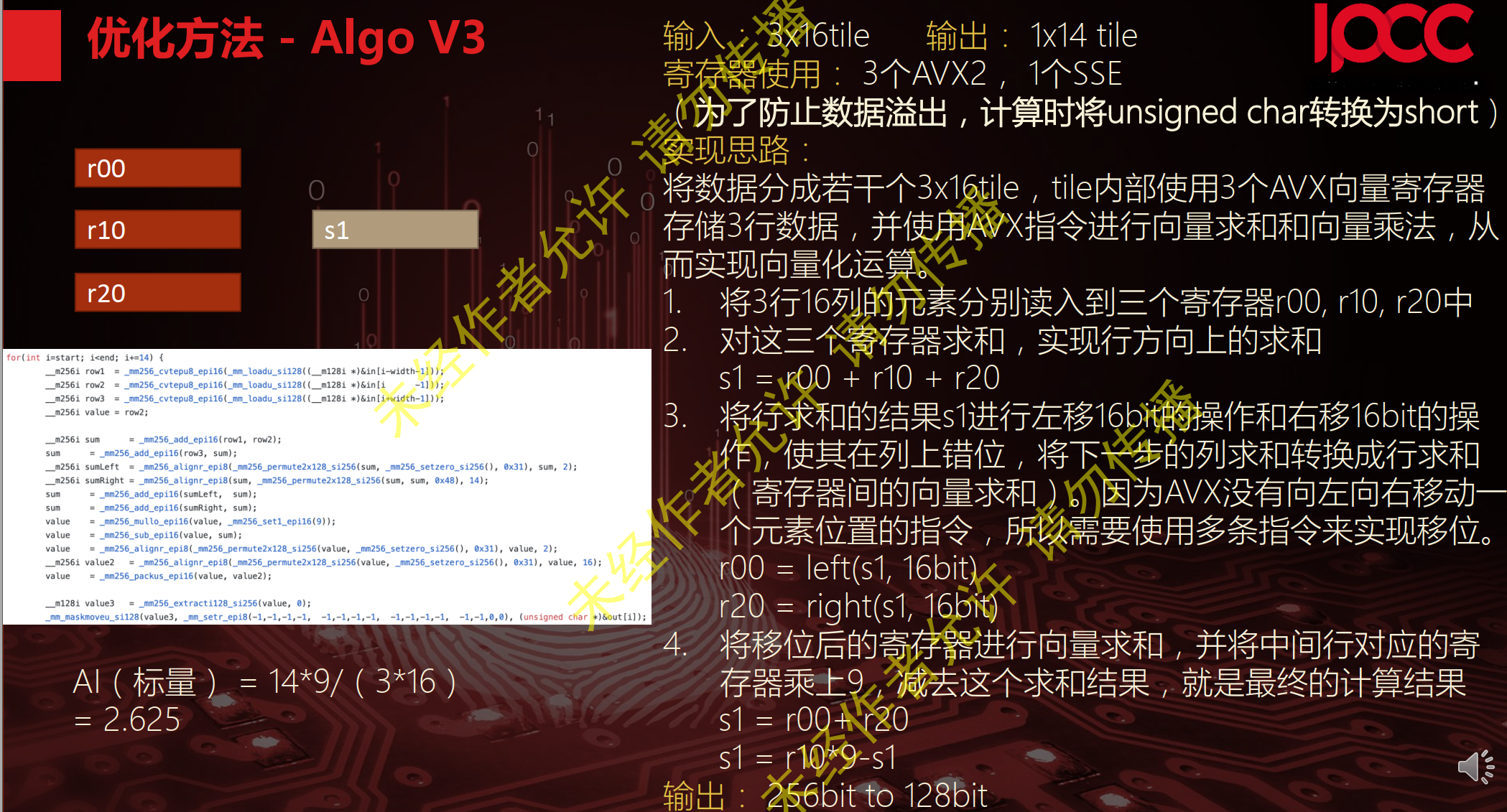

开启-O3选项,一般不用将代码改成多次计算和内存对齐。

开启-O3选项,一般不用将代码改成多次计算和内存对齐。

循环展开8次

循环展开8次

这个代码块只有执行代码分配在

这个代码块只有执行代码分配在 4. Environment Variance

1. 由于环境的影响,导致结果有个稳定的偏移。至少执行5次,展开16次的基本块。取最小的5次作为结果。

4. Environment Variance

1. 由于环境的影响,导致结果有个稳定的偏移。至少执行5次,展开16次的基本块。取最小的5次作为结果。

2. IACA 第二好的,在向量化类模拟的最好

3. llvm-mca 最差的,尤其是和loads有关时。

4. Ithemal 除了向量基本块都是最好的。在memory dependence (Ld/St)尤其好,但是向量基本块不好,可能与训练集没有向量基本块有关。

5. OSACA 第三。由于还在开发中,使用还遇到5个bug。在遇到一些不认识的指令的时候,会直接按照nops空指令处理。

3. Examples of Modeling Bugs

2. IACA 第二好的,在向量化类模拟的最好

3. llvm-mca 最差的,尤其是和loads有关时。

4. Ithemal 除了向量基本块都是最好的。在memory dependence (Ld/St)尤其好,但是向量基本块不好,可能与训练集没有向量基本块有关。

5. OSACA 第三。由于还在开发中,使用还遇到5个bug。在遇到一些不认识的指令的时候,会直接按照nops空指令处理。

3. Examples of Modeling Bugs 1. 最后一个例子是由于模型错误调度微指令导致的

2. Modeling bug due to unsigned division

1. 例子是 a 64-bit by 32-bit unsigned division.

1. 最后一个例子是由于模型错误调度微指令导致的

2. Modeling bug due to unsigned division

1. 例子是 a 64-bit by 32-bit unsigned division.

2. ???

2. ??? 3. Modeling bug due to zero-idioms

1.

3. Modeling bug due to zero-idioms

1.  2. 对这种结果固定的特殊指令的快速处理。

4. Modeling bug due to mis-scheduling

1. 对于数据依赖,上下指令的寄存器有写后读。

2. Ithemal’s and OSACA忽略了该依赖

3.

2. 对这种结果固定的特殊指令的快速处理。

4. Modeling bug due to mis-scheduling

1. 对于数据依赖,上下指令的寄存器有写后读。

2. Ithemal’s and OSACA忽略了该依赖

3.  4. llvm-mca 没有注意到(%rcx)是memory,没有依赖可以提前发射。

4. llvm-mca 没有注意到(%rcx)是memory,没有依赖可以提前发射。

吞吐量的计算(猜的)Skylake microarchitecture$

吞吐量的计算(猜的)Skylake microarchitecture$

what is aux mem?

what is aux mem?

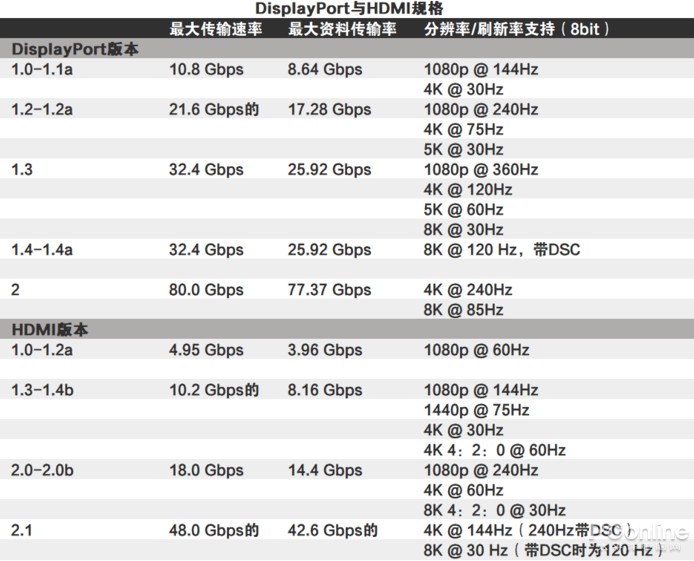

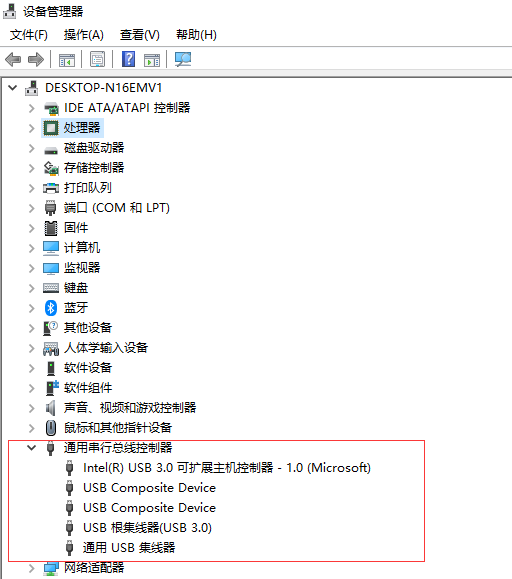

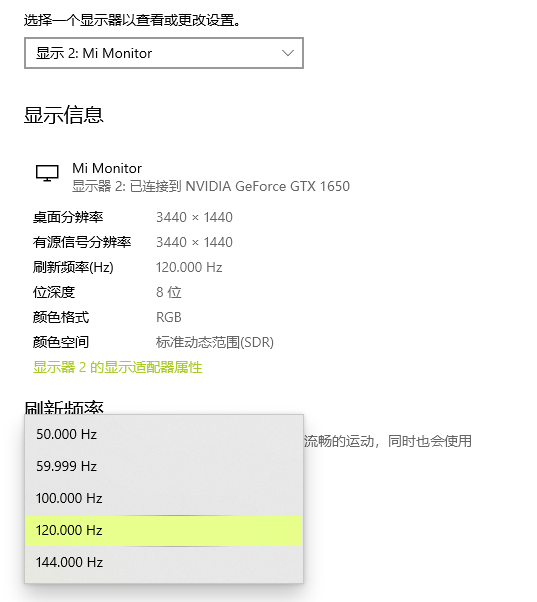

但是144Hz带不动,会花屏,或者闪烁。

但是144Hz带不动,会花屏,或者闪烁。