Microarchitecture: Zero (one) idioms & Mov Elimination

微架构的关系¶

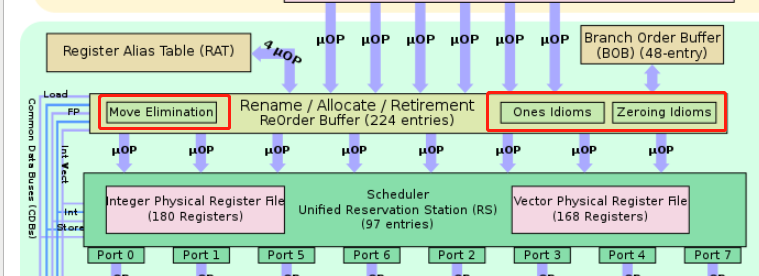

寄存器重命名是乱序执行Tomasulo算法的一部分

寄存器重命名可以实现: 1. 部分mov消除 2. NOPs 3. zero (one) idioms 对于这些指令,无序发射到scheduler。可以直接在reorder buffer写入结果。

Zero (one) idioms¶

Zero (one) idioms 是不管原寄存器src值是什么,结果/目的寄存器dst一直/一定是0 (1)的一类指令。比如:XOR一个寄存器和自己。

- 由于是在寄存器重命名阶段(Rename)时实现的

- 所以不需要发射到port执行单元执行,占用硬件资源。也没有延迟

- 但是需要划分前面部分的decode的带宽,和ROB(reorder buffer)的资源

例子¶

由于第一条指令是Zero idioms;后两条指令可以macro-fusion。所以各部分平均执行次数为

| 指令个数 | UOPS_ISSUED | UOPS_EXECUTED | UOPS_RETIRED |

|---|---|---|---|

| 3 | 2 | 1 | 2 |

特殊的情况¶

有些架构可能不支持srcImm0-dstReg的指令的Zero idioms

mov Elimination¶

1. 由于是在寄存器重命名阶段(Rename)时实现的

1. 所以不需要发射到port执行单元执行,占用硬件资源。也没有延迟

2. 但是需要划分前面部分的decode的带宽,和ROB(reorder buffer)的资源

1. 由于是在寄存器重命名阶段(Rename)时实现的

1. 所以不需要发射到port执行单元执行,占用硬件资源。也没有延迟

2. 但是需要划分前面部分的decode的带宽,和ROB(reorder buffer)的资源

例子¶

由于第二条指令是mov Elimination;后两条指令可以macro-fusion。所以各部分平均执行次数为

| 指令个数 | UOPS_ISSUED | UOPS_EXECUTED | UOPS_RETIRED |

|---|---|---|---|

| 5 | 4 | 3 | 4 |

被覆盖的结果是否能消除¶

第一个mov被覆盖了。这是属于编译器的工作。CPU做不到这点(即使做得到,为了实现这点设计的硬件开销也会很大,不值得)无效操作是否能消除¶

一般和0的立即数作用有关

第二条指令在IvyBridge也不会消除。这同样是编译器的工作但是llvm-mca通过ZeroRegister的实现,可以消除。

类似的还有

一般也不会消除。这同样是编译器的工作需要进一步的研究学习¶

暂无

遇到的问题¶

暂无

开题缘由、总结、反思、吐槽~~¶

参考文献¶

https://randomascii.wordpress.com/2012/12/29/the-surprising-subtleties-of-zeroing-a-register/

https://easyperf.net/blog/2018/04/22/What-optimizations-you-can-expect-from-CPU

https://zh.m.wikipedia.org/zh-hans/%E5%AF%84%E5%AD%98%E5%99%A8%E9%87%8D%E5%91%BD%E5%90%8D