RISC-V

RISC-V and ARM¶

RISC-V是完全开源的,虽然现在编译器和IDE生态还不行,但是在各国的大力推动下,未来可期。

相比於Arm架構,RISC-V的指令集更小、可以模組化擴充、客製化設計自由度等優點,經過數年發展,漸成為Arm架構的有力挑戰者。

RISC-V现在在物联网的应用是很好的。

The RISC-V Instruction Set Manual¶

多种不同长度的ISA¶

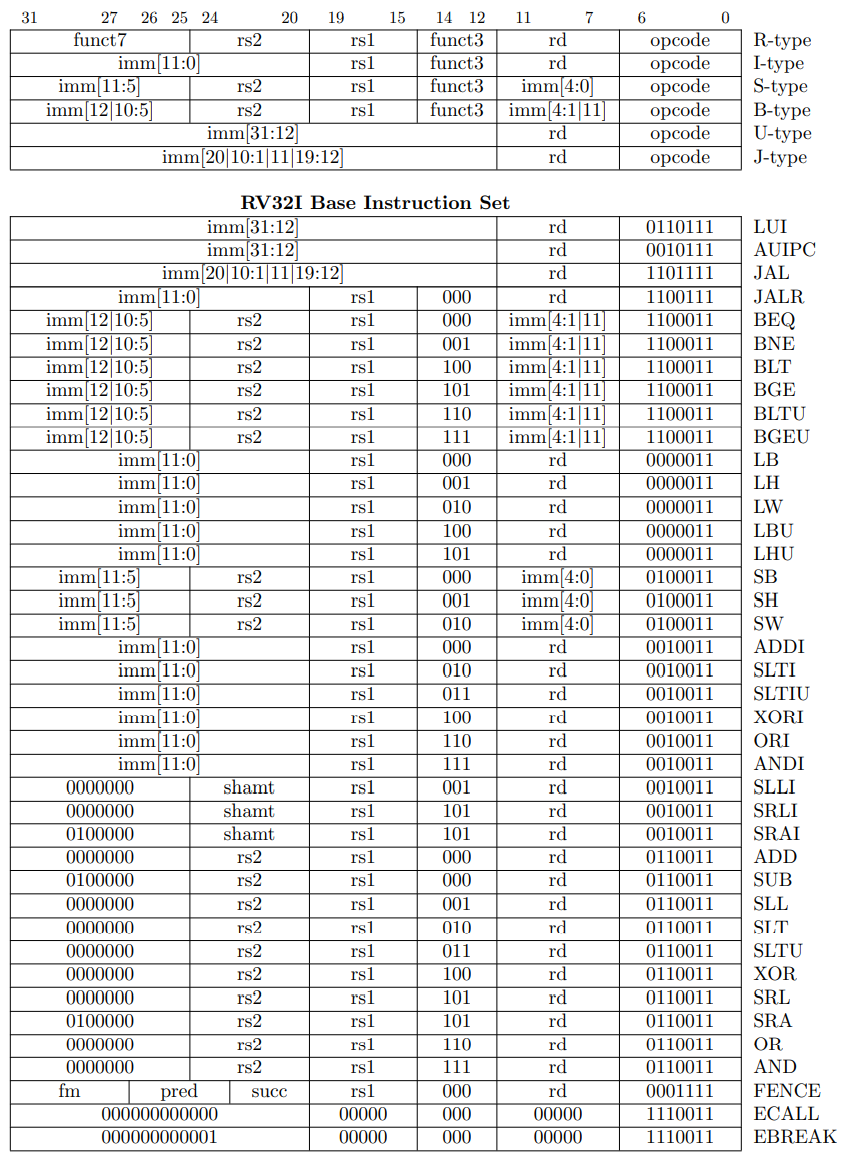

RV32I base integer instruction set.¶

RV32I contains 40 unique instructions.

For RV32I, the 32 x registers are each 32 bits wide,

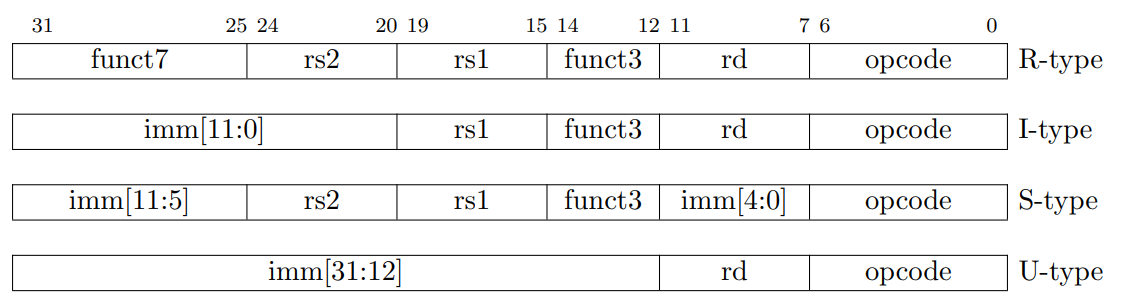

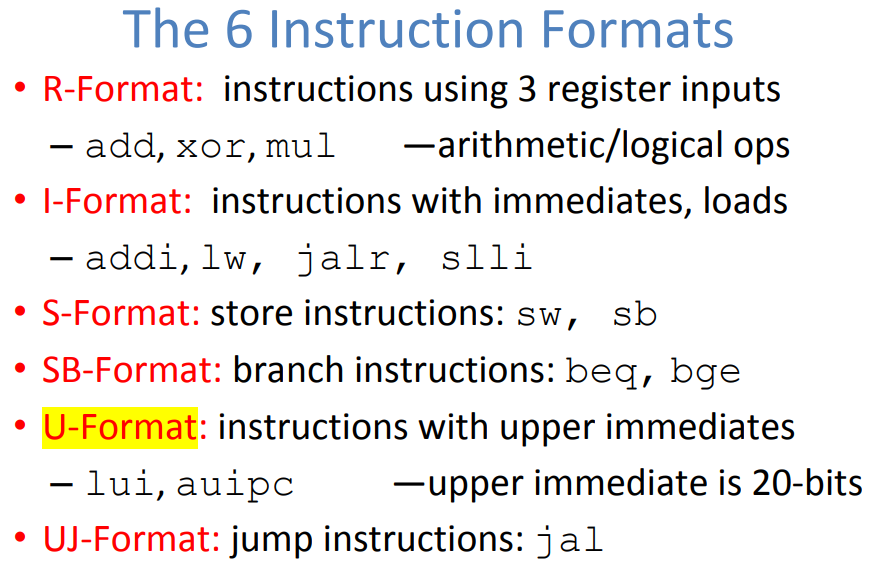

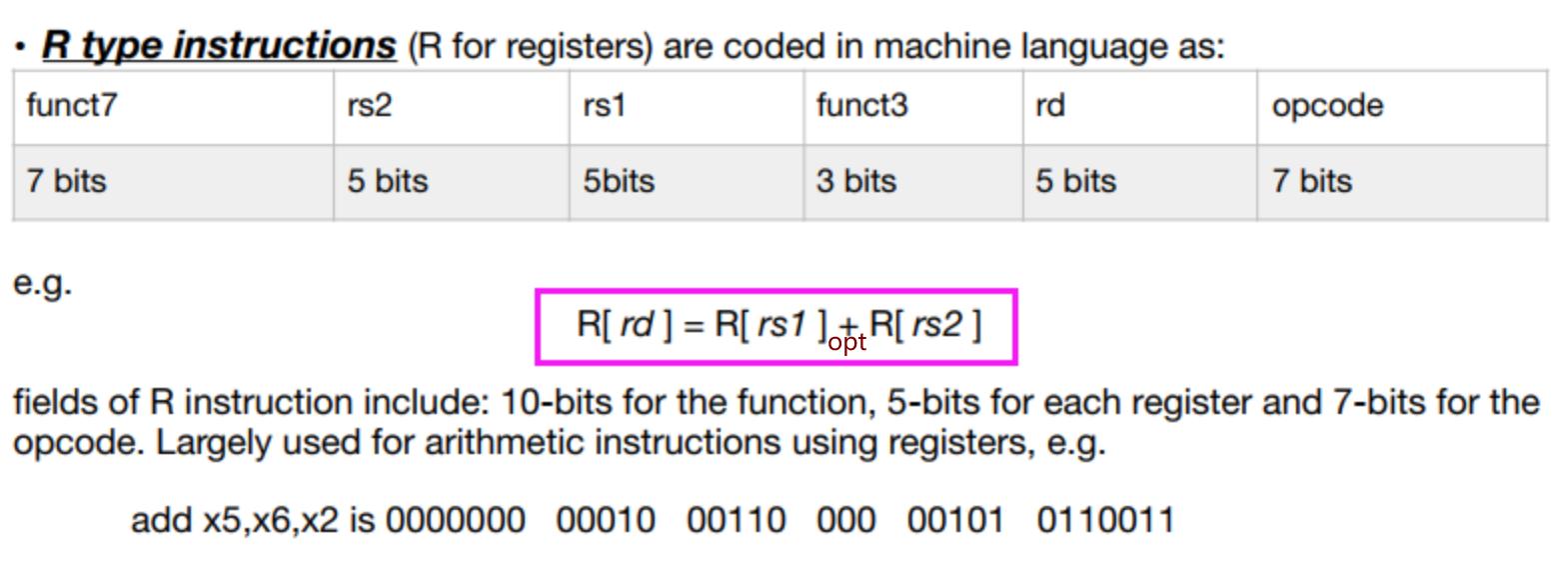

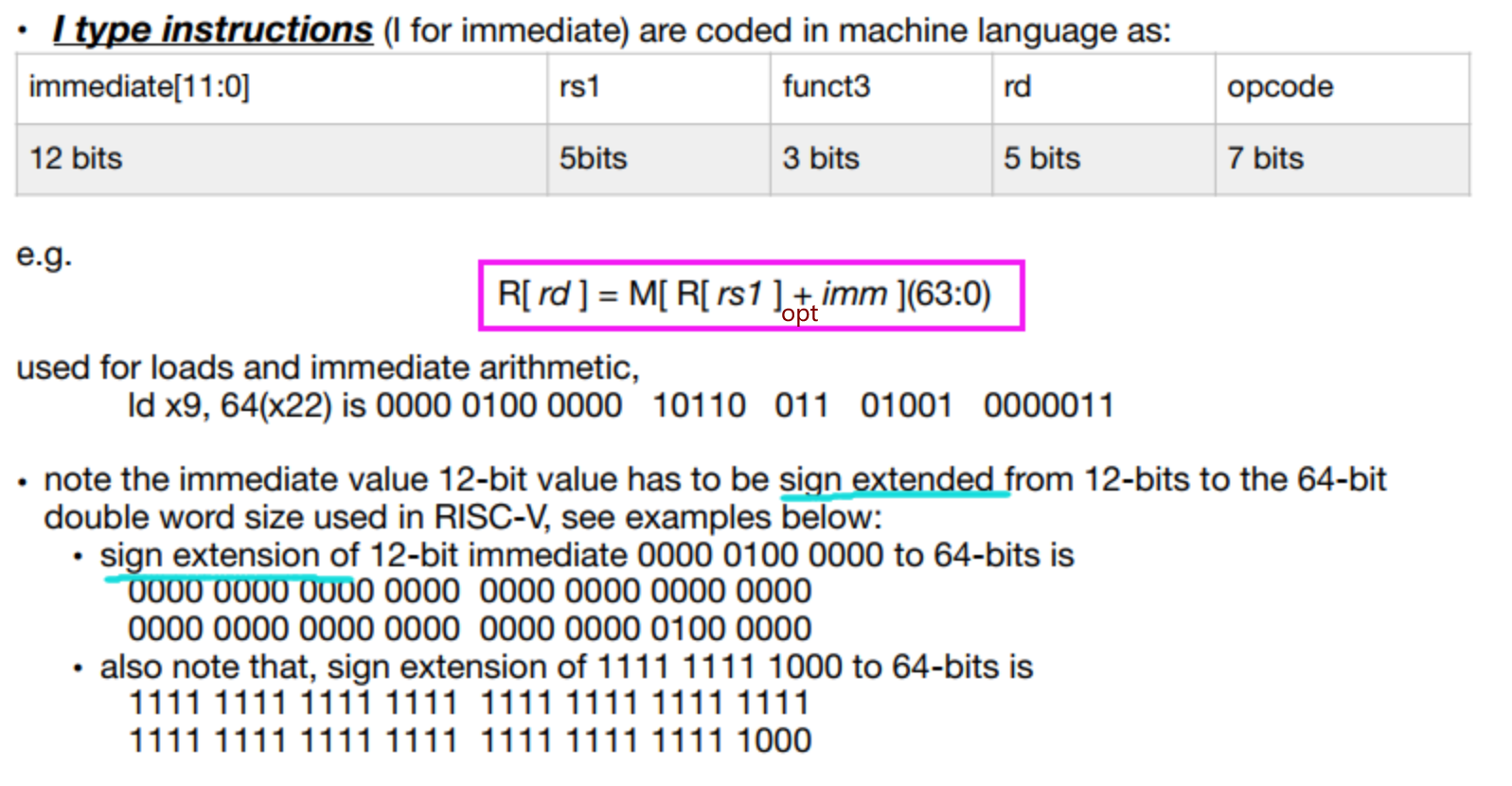

Base Instruction Formats:¶

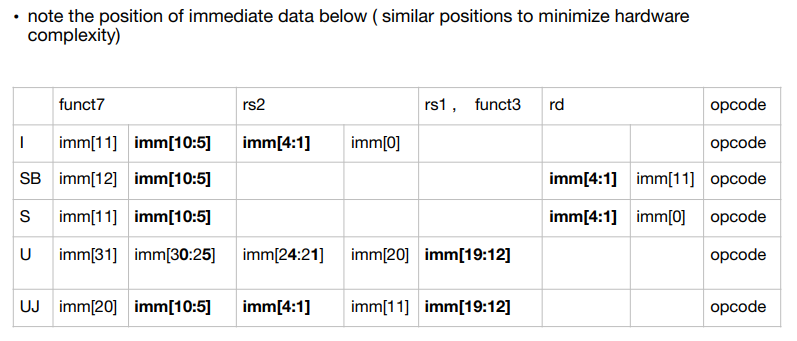

最先是符号位的原因是,立即数是二进制补码表示,也就是有负数的,所以有addi指令但是没有subi指令

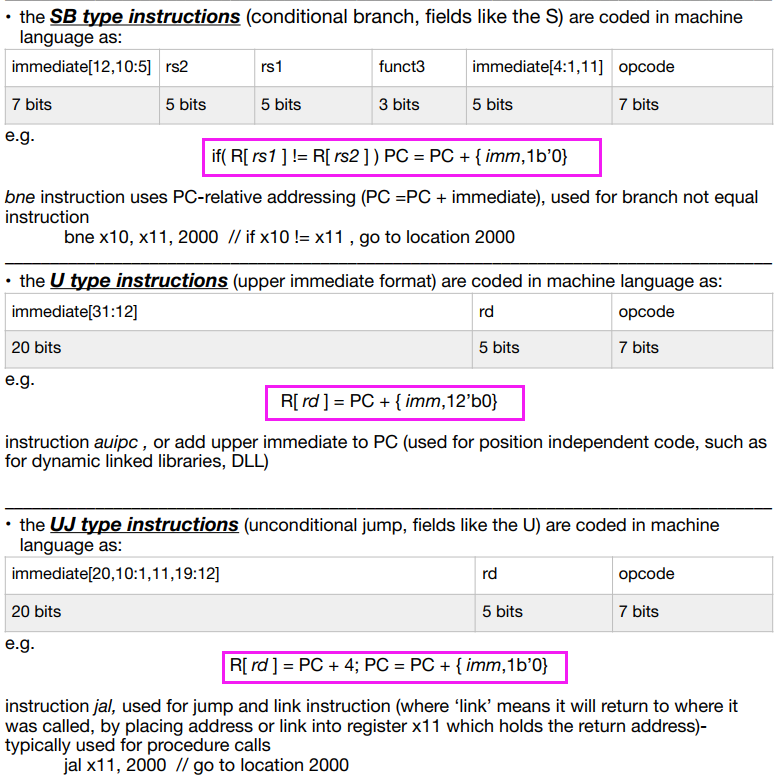

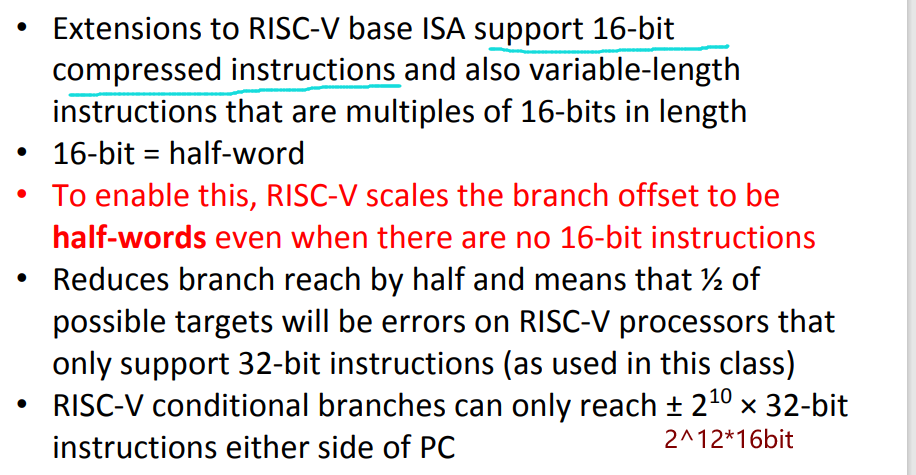

为什么跳转的时候,最低位为0。为了支持RVC

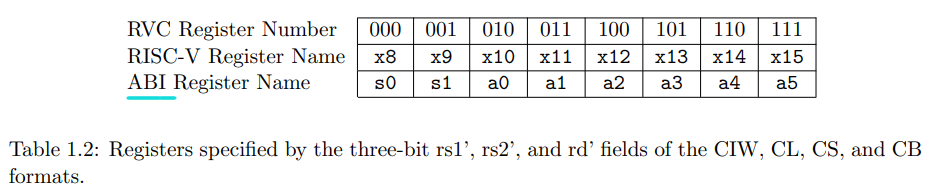

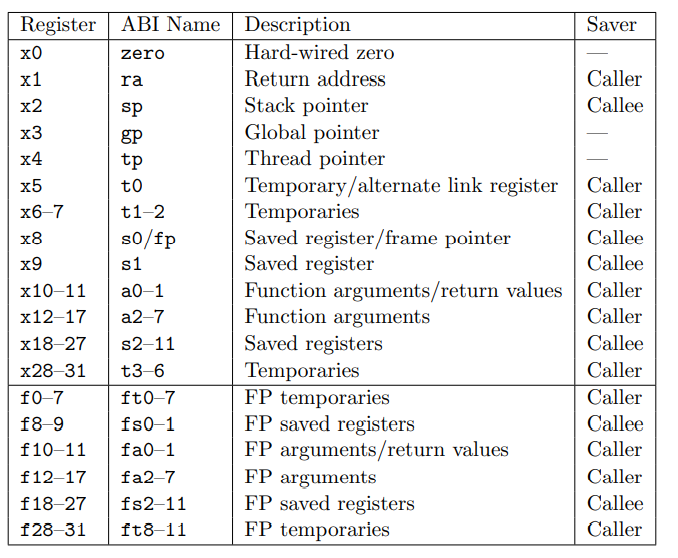

application binary interface(ABI)

RV32E Base Integer Instruction Set( draft)¶

reduced version of RV32I designed for embedded systems. The only change is to reduce the number of integer registers to 16.

RV64I Base Integer Instruction Set¶

builds upon the RV32I variant。需要注意的一点,是访问的寄存器和寄存里的地址变成64位了,指令长度还是32位。

register: RV64I widens the integer registers and supported user address space to 64 bits

如果想要在RV64I里运行32位的指令,在指令后加后缀W就行。比如ADDIW

Additional instruction variants are provided to manipulate 32-bit values in RV64I, indicated by a ‘W’ suffix to the opcode.These “*W” instructions ignore the upper 32 bits of their inputs and always produce 32-bit signed values,

访存相关¶

The LD instruction loads a 64-bit value from memory into register rd for RV64I.

The LW instruction loads a 32-bit value from memory and sign-extends this to 64 bits before storing

it in register rd for RV64I. The LWU instruction, on the other hand, zero-extends the 32-bit value

from memory for RV64I. LH and LHU are defined analogously for 16-bit values, as are LB and

LBU for 8-bit values. The SD, SW, SH, and SB instructions store 64-bit, 32-bit, 16-bit, and 8-bit

values from the low bits of register rs2 to memory respectively.

RV128I Base Integer Instruction Set¶

寄存器位数和地址空间变成128位。

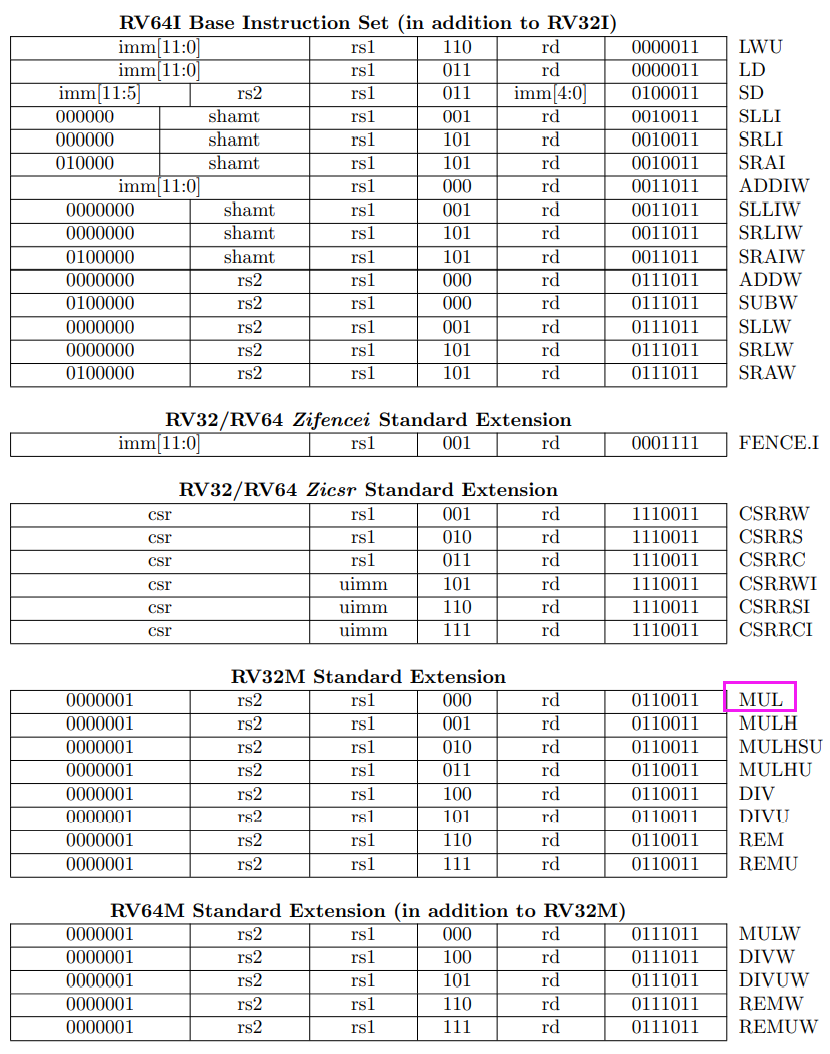

Standard Extension for¶

- Integer Multiplication and Division

- MULDIV

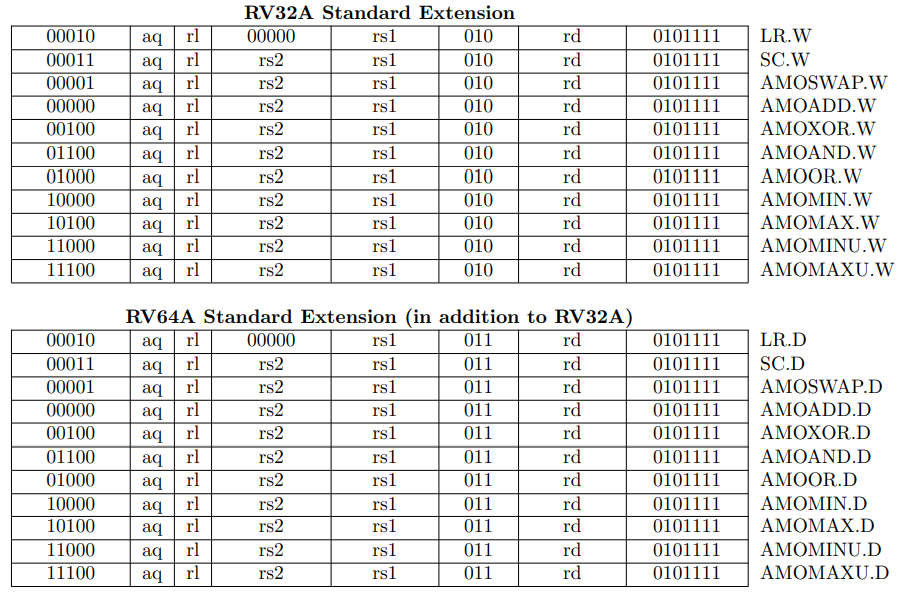

- Atomic Instructions

- CSR Instructions

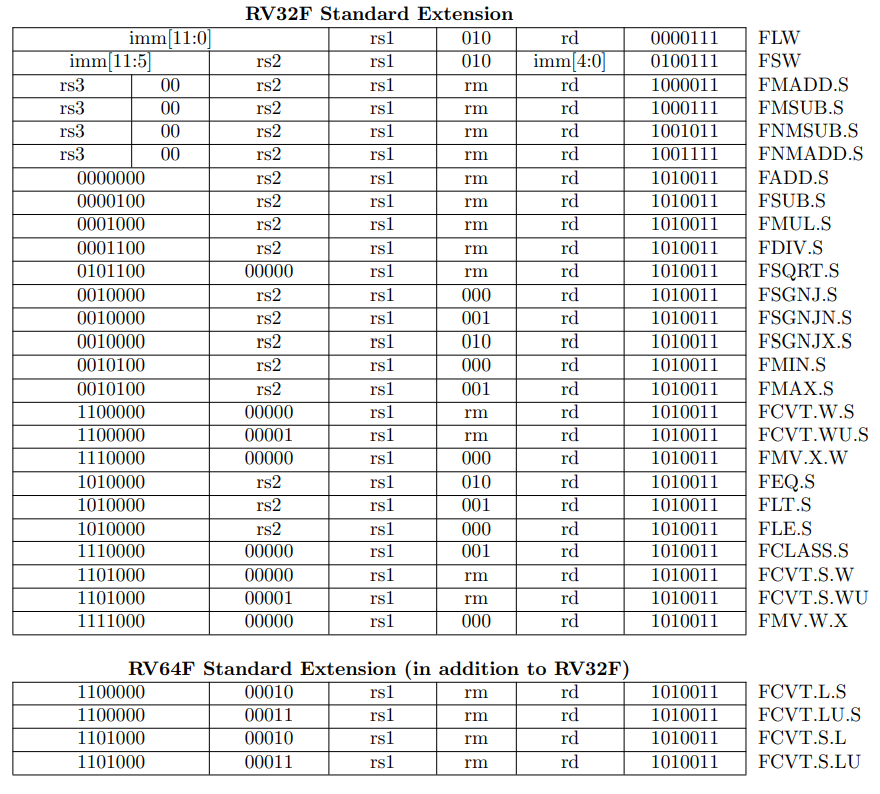

- Single-Precision Floating-Point

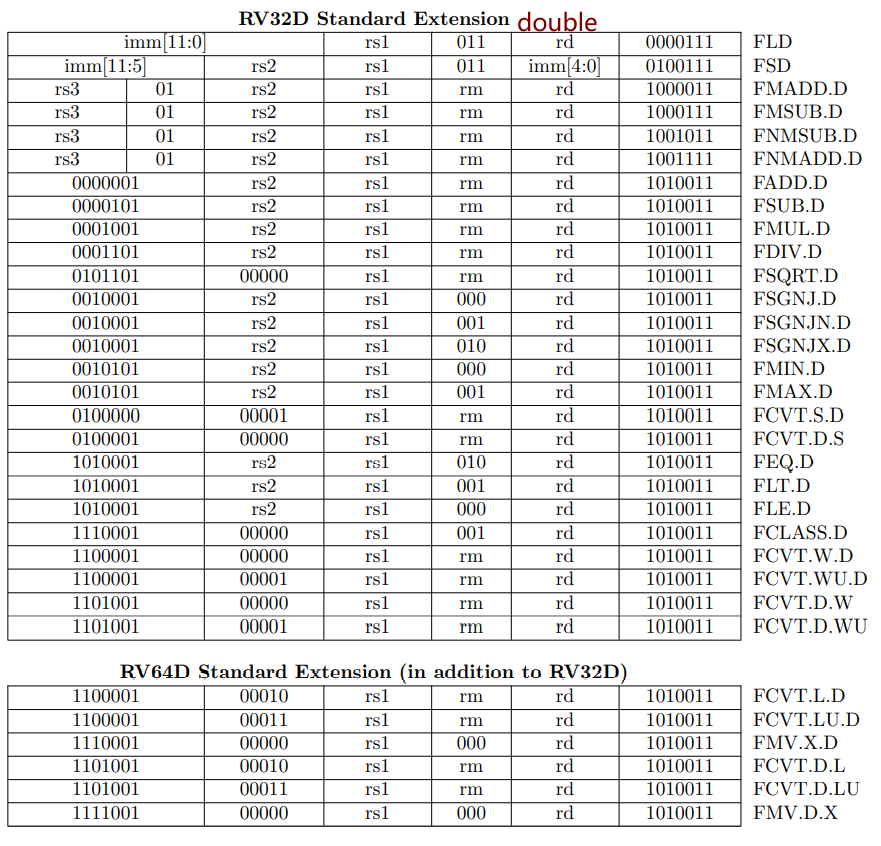

- Double-Precision Floating-Point

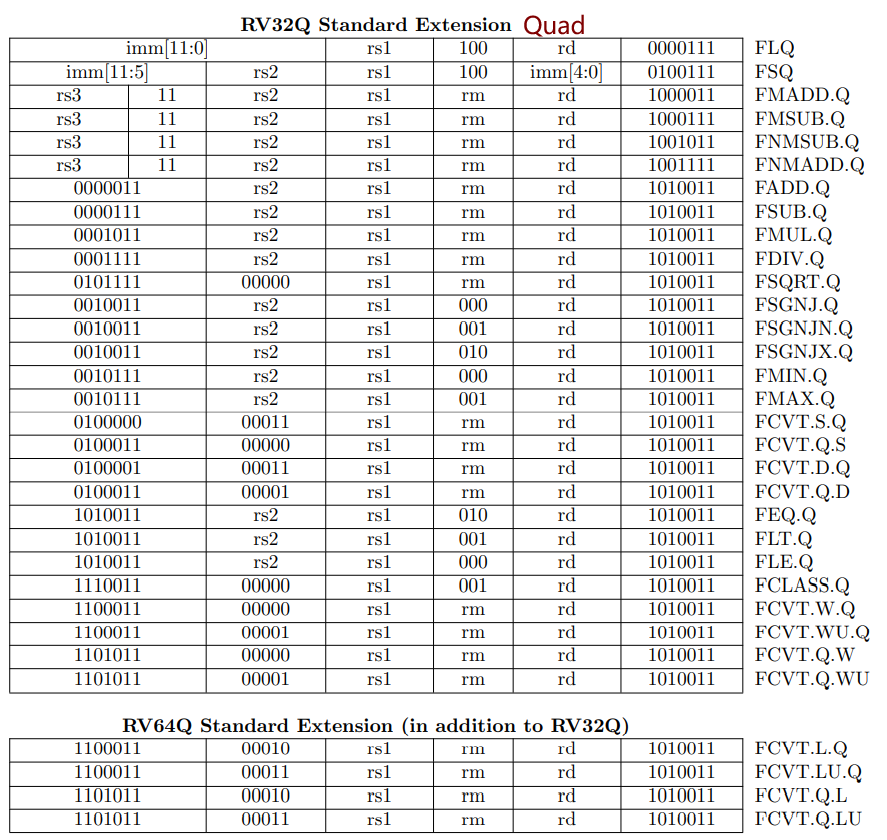

- Quad-Precision Floating-Point

- Bit Manipulation

- Vector Operations(draft)

指令速查¶

RISC-V assembly syntax¶

beq rs1, rs2, Label #RISC-V

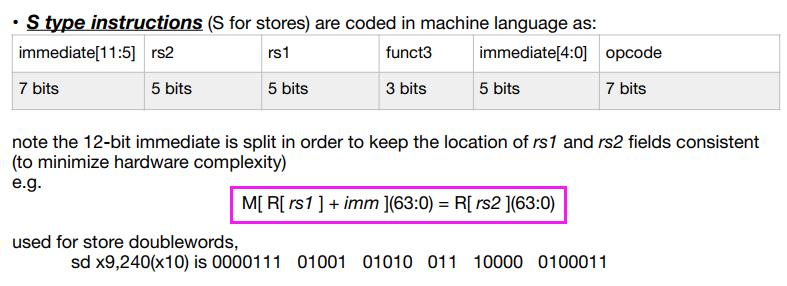

SW rs2, imm(rs1) # Mem[rs1+imm]=rs2 ,汇编将访存放在最后

add rd, rs1, rs2 # rd = rs1 + rs2

Registers¶

frame pointer = BP in X86

ra = Link register in ARM

Some RISC-V compilers use a frame pointer, fp, or register x8 to point to first double word of frame.

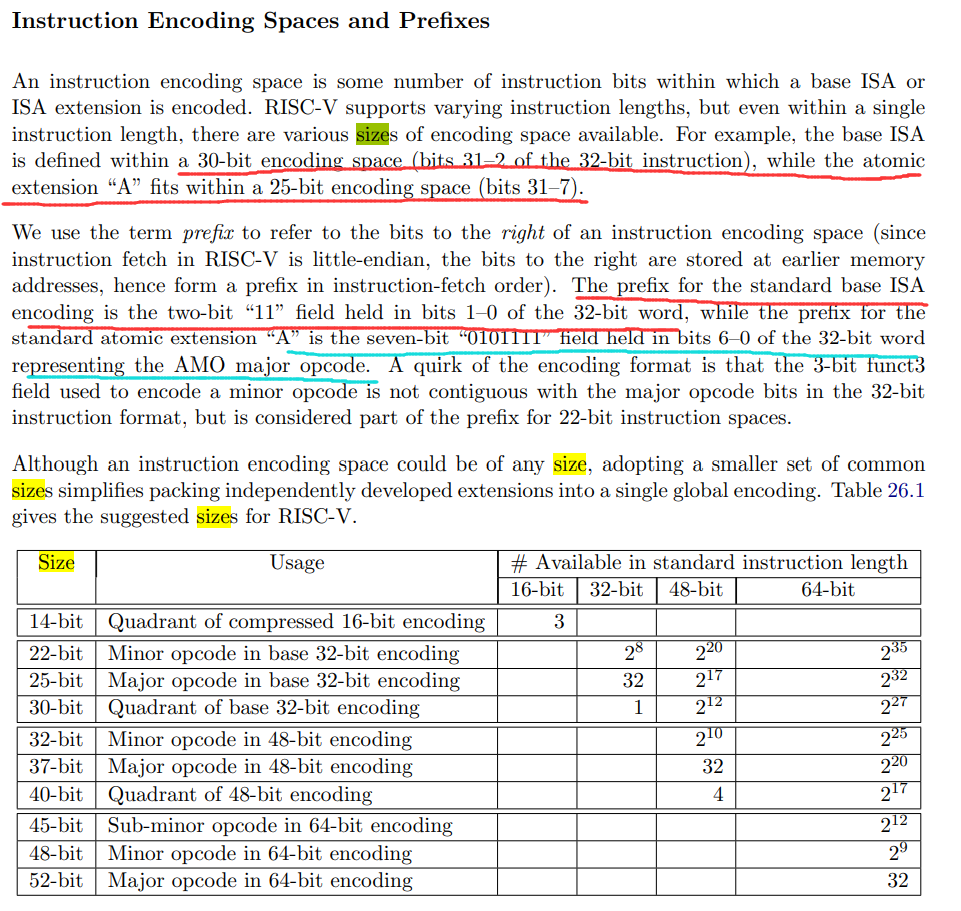

指令设计¶

先用高维,预留低位来拓展

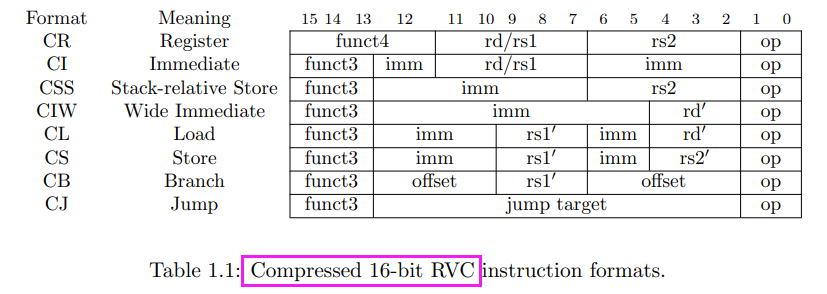

RVC (compressed)

32位时

minor 不包括func3 + opcode (去除固定2位)

major没func3

compiler explorer¶

编译器模拟器

https://godbolt.org/

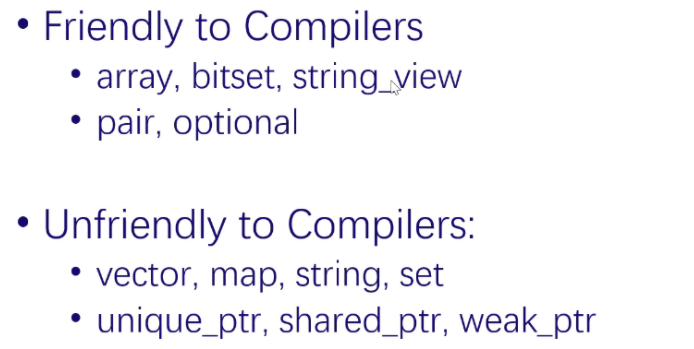

array由于大小是一开始固定好的,分配在栈里。而vector是变的,分配在堆里?

RISC-V环境搭建¶

https://chivier.github.io/2022/02/04/2022/2202-QemuTest/

但是RVV向量化在git其他分支里,gcc7和8编译不会错

需要进一步的研究学习¶

Control and Status Registers (CSRs)

遇到的问题¶

暂无

开题缘由、总结、反思、吐槽~~¶

参考文献¶

无